# 中華民國第 65 屆中小學科學展覽會

## 作品說明書

高級中等學校組 工程學科(一)

第三名

052309

前瞻奈米片場效電晶體設計之最佳化

學校名稱： 臺北市立第一女子高級中學

|        |       |

|--------|-------|

| 作者：    | 指導老師： |

| 高二 陳玟霖 | 黃光照   |

關鍵詞： 奈米片、電晶體、最佳化

## 摘要

在科技進步的年代，電晶體成為組成高效能晶片不可或缺的元件，其發展影響著電子產品的效能與功耗。隨著製程技術節點縮小至 2nm 以下，傳統鳍式場效電晶體（FinFET）架構逐漸面臨短通道效應與漏電流增加等挑戰，而環繞式閘極場效電晶體（GAAFET）技術則因其優異的電流控制能力與低功耗特性，成為新一代電晶體的主流。本研究探討在固定有效寬度與垂直間距的條件下，不同奈米片堆疊數量對電晶體電性的影響，透過科技電腦輔助設計（TCAD）軟體模擬分析次臨界擺幅（SS）與臨界電壓（ $V_t$ ）等參數，對下世代環繞式閘極奈米片場效應電晶體(NSFET)進行最佳化研究，提供未來半導體技術發展之設計方針。

# 壹、 前言

## 一、研究動機

在現代社會，電子科技的快速進步影響了人類生活的方方面面。從日常使用的智慧型手機、電腦，到推動工業與科技發展的人工智慧（AI）運算平台和高速數據中心，這些科技產品的核心元件無不依賴於電晶體技術的突破與演進。電晶體作為現代電子產品的基石，其運作特性不僅決定了數位訊號（0 與 1）的傳輸能力，更在訊號放大與低功耗運算中扮演著重要角色。

在高中物理課程中，我首次接觸到電晶體（Transistor）這一電子元件。課程中介紹了金氧半場效電晶體（MOSFET）的基本結構，包括 NMOS（n-type）與 PMOS（p-type），以及其作為邏輯閘與電子開關的基本運作原理。同時，也認識到摩爾定律（Moore's Law）在推動電子元件發展中的關鍵角色。

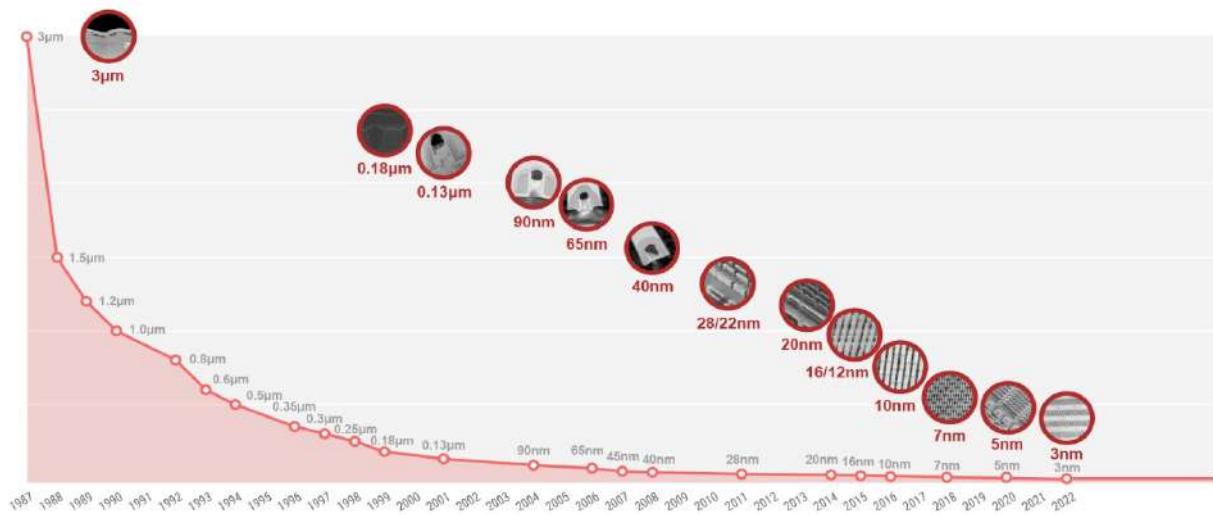

摩爾定律指出，在成本相近的情況下，單位晶片面積內的電晶體數量大約每兩年會增加一倍，帶動晶片效能與密度持續提升。為了實現這一趨勢，電晶體尺寸需不斷微縮，製程技術亦持續演進，從早期的 90 奈米、45 奈米節點，逐步進入 16 奈米、7 奈米，直至現今已量產的 3 奈米技術。

圖（一）為邏輯製程技術時間軸，展示了從 3 微米至 2 奈米等技術節點的演進過程，體現了摩爾定律所預測的晶體管密度提升趨勢。【擷取自 TSMC 官網】

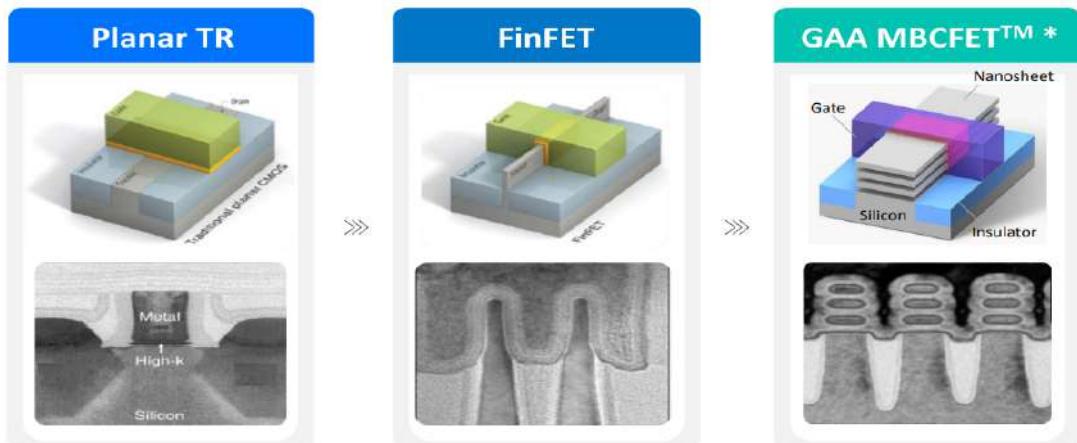

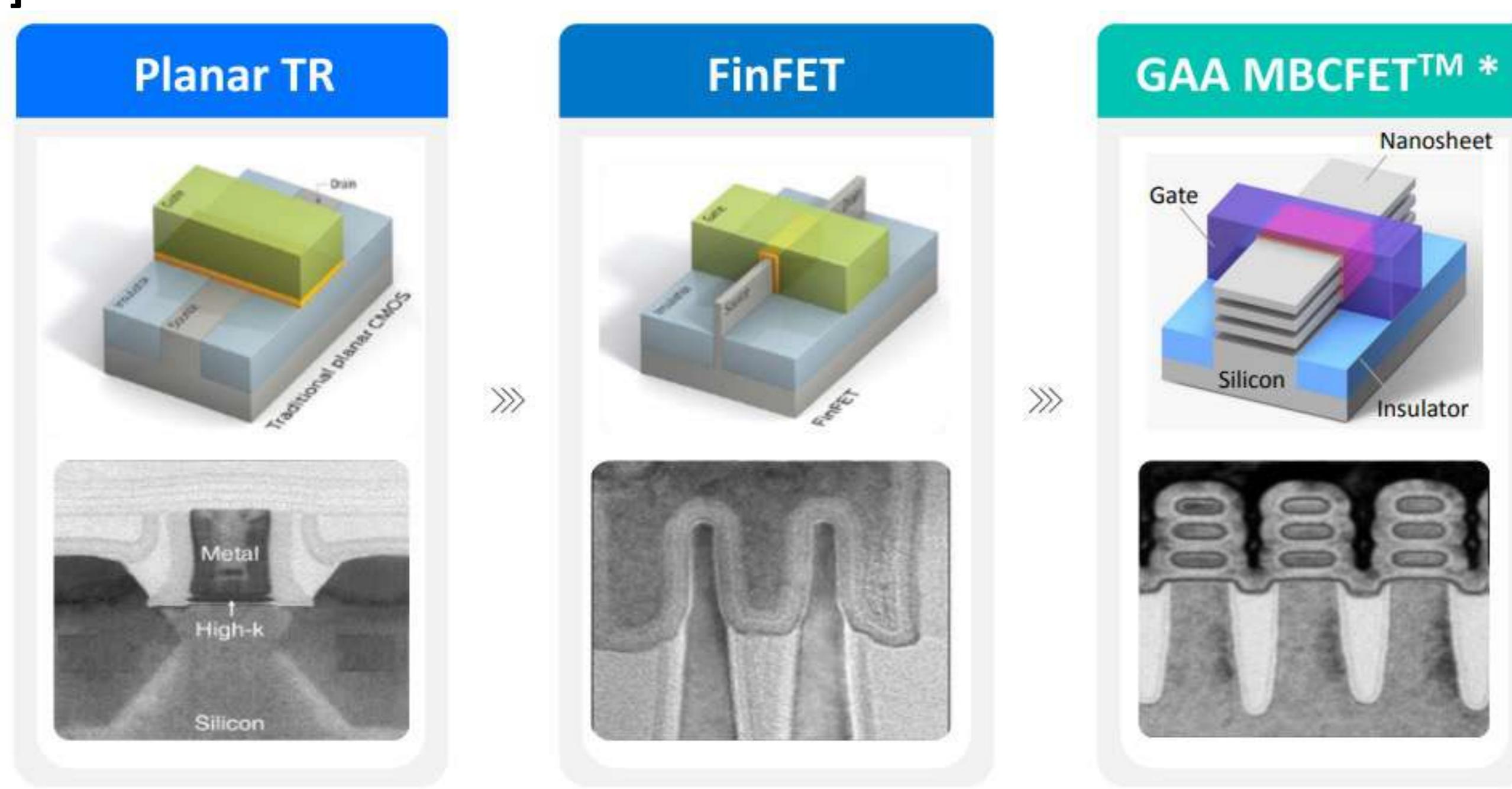

然而，隨著技術接近物理極限，漏電流增加與功耗問題成為了阻礙進一步發展的主要挑戰。在此背景下，環繞式閘極技術（GAA，Gate-all-Around）應運而生。這種新型結構通過全方位包覆通道的設計，大幅提升了電晶體的控制能力，成功降低了漏電效應，並將首次於台積電的 2 nm 製程節點中投入商業化，展現出其巨大的潛力。然而，即使是 GAA 技術，在進一步縮小至 1.5 nm 技術節點時，仍面臨著設計與製程的巨大挑戰。因此，設計出電晶體的最佳化參數，已成為一項重要且尚未解決的挑戰。

圖（二）先進邏輯元件架構演進示意：從平面電晶體到多層奈米片 GAA 技術。

【擷取自 Evolution of logic devices. Reproduced with permission.[30]

Copyright 2022, IEEE.】

面對這些複雜的挑戰，電晶體模擬的重要性便突顯出來。在實際製程中，每一次設計更改和參數調整都耗時且成本高昂。透過精確的物理模型和數值演算法，模擬能夠在實際製造之前，預測電晶體在不同設計參數下的電氣特性，例如電流、電壓、功耗等。這使得我們能在虛擬環境中，快速迭代並探索大量的設計可能性，有效縮短研發週期並降低開發成本。

透過對電晶體結構、材料特性以及操作條件進行深入的模擬研究，我們可以更精確地找出最佳化參數。這不僅能幫助克服目前 GAA 技術在微縮至 1.5 奈米所面臨的挑戰，也能為未來新興電晶體技術（例如奈米片電晶體或碳奈米管電晶體）的開發提供重要的理論依據與設計指引。因此，我希望建立一個開放式的模擬平臺，為解決電晶體微縮與效能提升的瓶頸問題，貢獻一份心力。

## 二、研究目的

近年來環繞式閘極場效電晶體 (GAAFET)，或稱為奈米片場效電晶體 (Nanosheet FET, NSFET)，受到廣泛的注目，不同於以往的 FinFET，GAAFET 可在對電晶體通道環繞式的完全包覆，因此可控制通道導通電流的面積更大，同時環繞式閘極結構的電晶體還有：(1) 更高的電流控制能力 (2) 更低的功耗 (3) 有效抑制短通道效應，提升性能與穩定性……等優點。

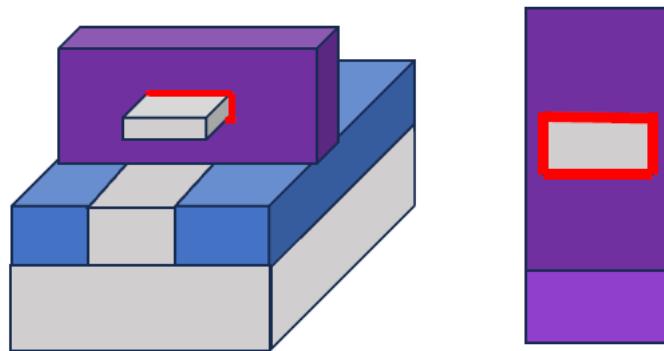

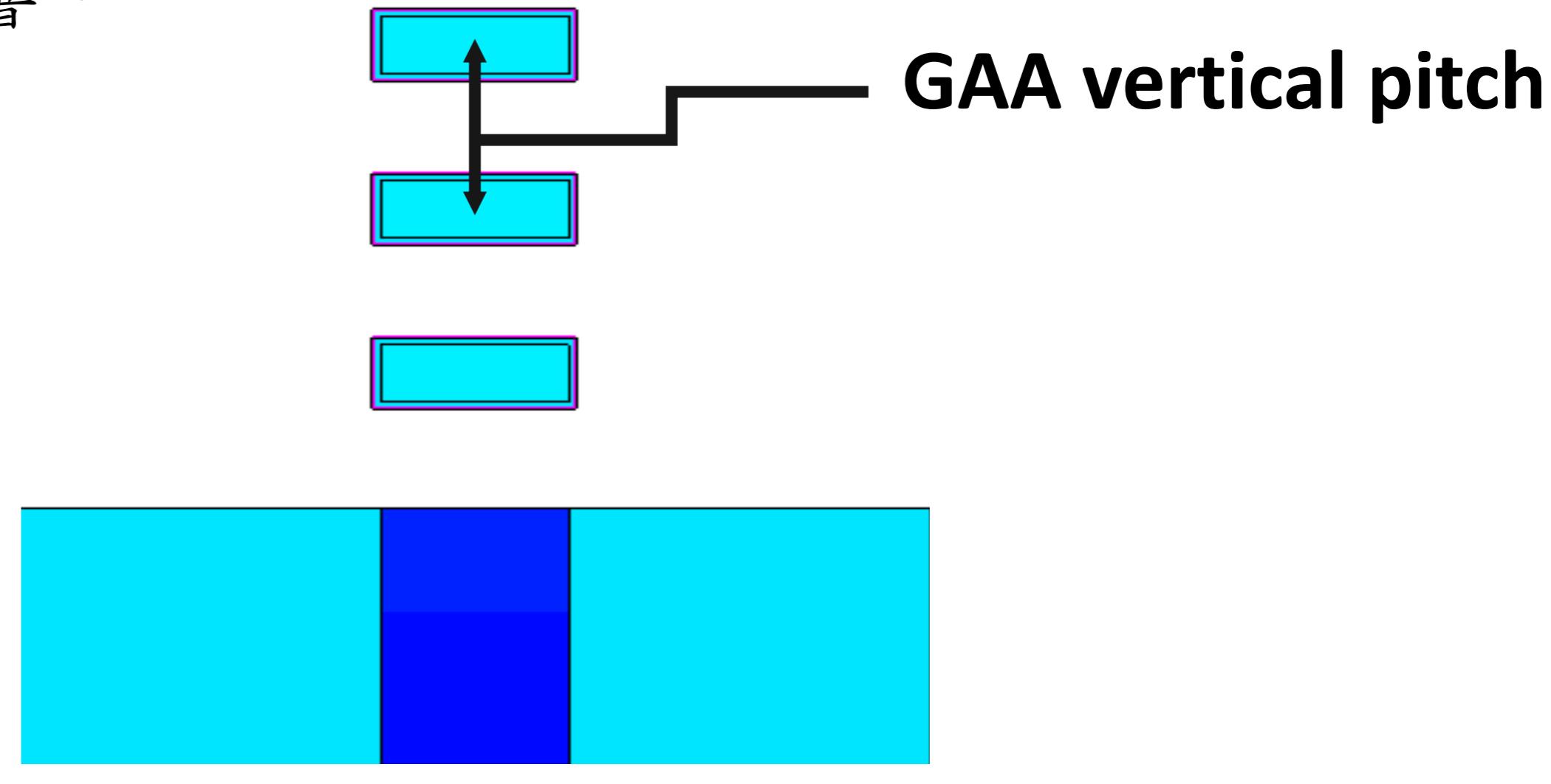

本次實驗研究目的主要為：探討在固定有效寬度 (Effective width) 及環繞式閘極垂直間距 (GAA Vertical Pitch) 下，改變奈米片的數量對 GAAFET 電性的影響。

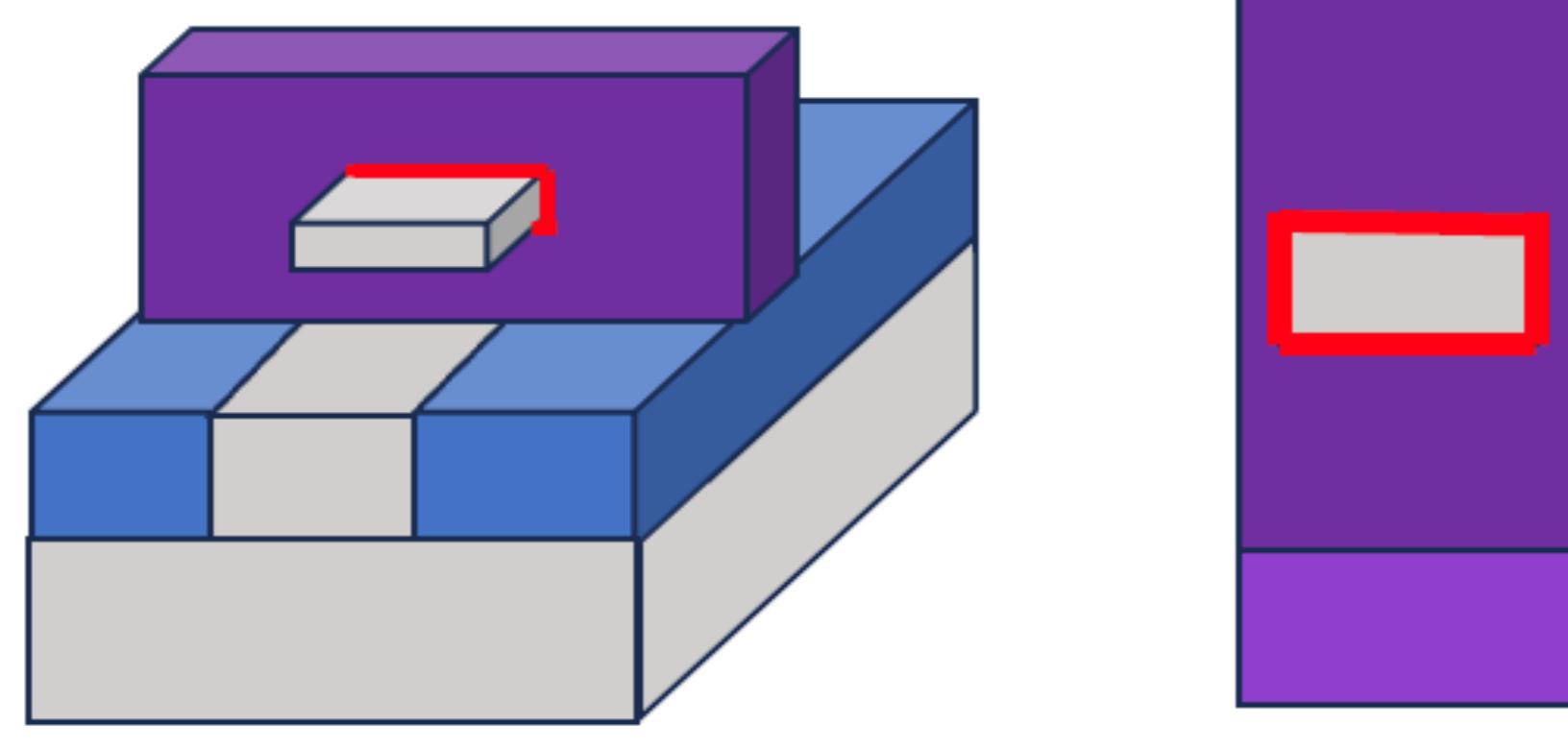

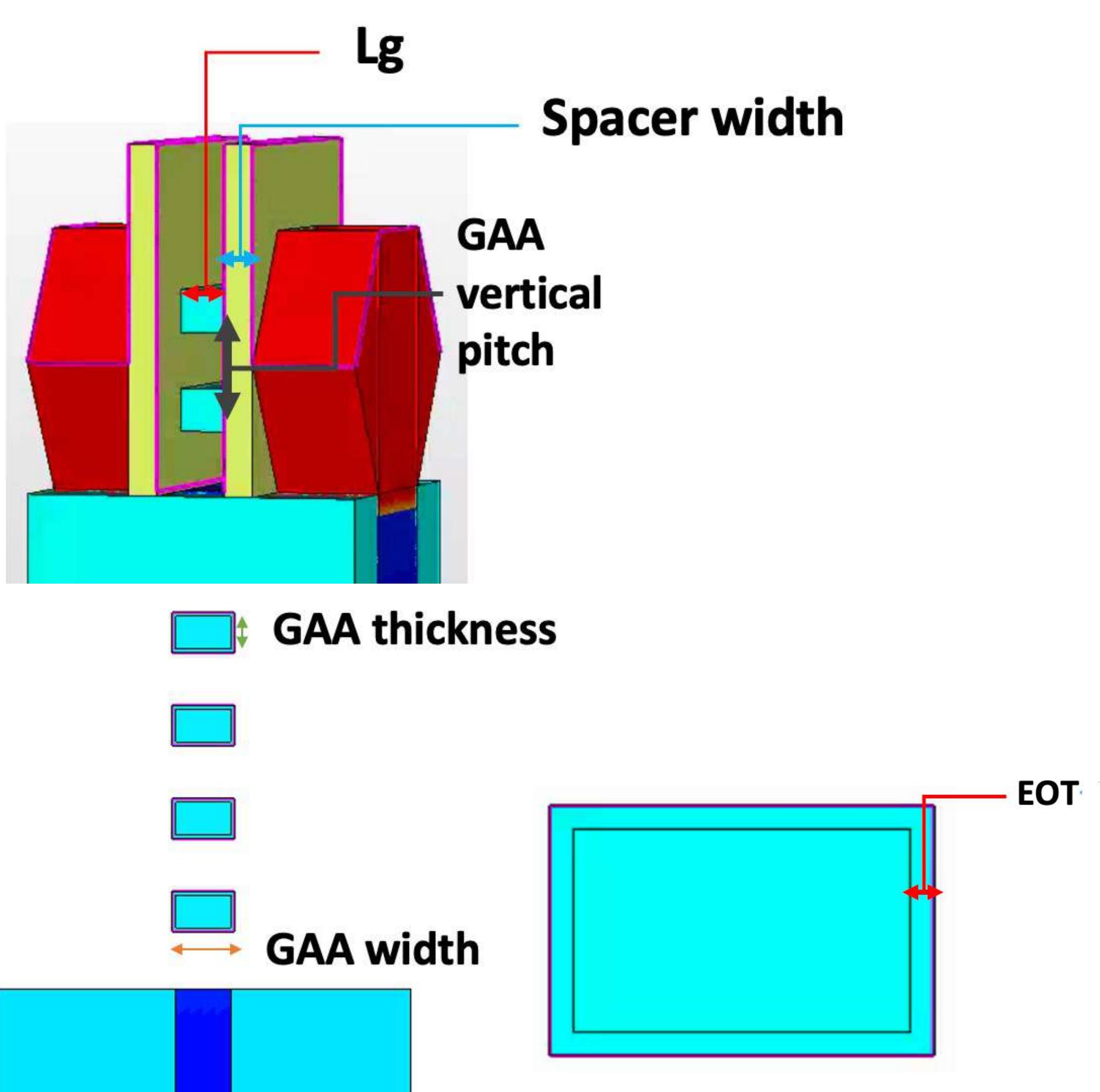

圖（三）GAAFET 結構示意圖，紅色框線為閘極與通道接觸之有效寬度，增加有效寬度可提升電晶體的導通電流。【使用 Microsoft PowerPoint 軟體繪製】

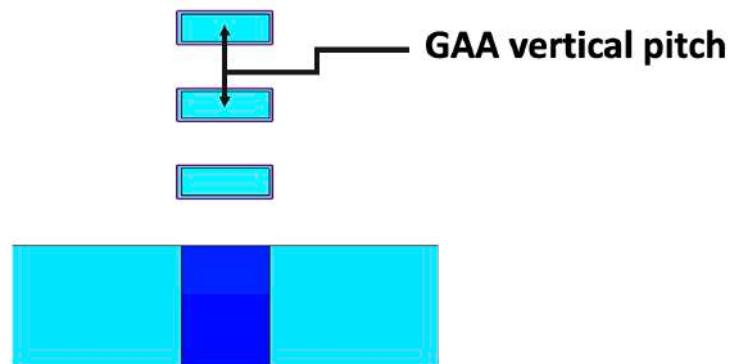

圖（四）為 GAA vertical pitch 示意圖

【擷取自 Sentaurus TCAD 模擬結果，並以 Microsoft PowerPoint 軟體標註】

### 三、文獻回顧

#### (一) IRDS Roadmap 2023 Device Ground Rules : IRDS (國際半導體元件與系統路線

圖)是由 IEEE( Institute of Electrical and Electronics Engineers ) 下屬的 Semiconductor Industry Association (SIA) 發起並協調的國際合作計劃白皮書。IRDS 針對半導體產業未來發展的各個層面，從製程技術、材料創新、設計規範到裝置架構等，提供清楚的方向與策略建議。每年更新的路線圖包括對各類半導體元件、系統架構的深入預測，並強調技術創新所需克服的挑戰，以及如何在摩爾定律漸進放緩的背景下，達到性能和成本的平衡，幫助調整產品策略和技術研發方向。

1. Device Architecture and Ground Rules Roadmap for Logic Devices (邏輯元件的架構與製程基準路線圖)：分析邏輯元件從 FinFET、GAAFET 到互補式場效電晶體 (CFET) 的結構演進，探討閘極長度、驅動電流與功耗的變化趨勢。

2. Projected Electrical Specifications of Logic Core Device：分析未來邏輯核心元件的驅動電流、次臨界擺幅(SS)、功耗等電性，並探討新材料與先進製程對晶片效能的影響。

| YEAR OF PRODUCTION                                    | 2028                                                                                  |

|-------------------------------------------------------|---------------------------------------------------------------------------------------|

| Logic industry "Node Range" Labeling                  | 2028-LGAA                                                                             |

| Fine-pitch 3D integration scheme                      | G42M16<br>"4.5nm"<br>Stacking                                                         |

| Logic device structure options                        | LGAA                                                                                  |

| Backside structure options                            | Direct contact                                                                        |

| Platform device for logic                             | LGAA                                                                                  |

|                                                       |  |

| LOGIC DEVICE GROUND RULES                             |                                                                                       |

| Mx pitch (nm)                                         | 20                                                                                    |

| M1 pitch (nm)                                         | 21                                                                                    |

| M0 pitch (nm)                                         | 16                                                                                    |

| Gate pitch (nm)                                       | 42                                                                                    |

| Lg: Gate Length - HP (nm)                             | 12                                                                                    |

| Lg: Gate Length - HD (nm)                             | 12                                                                                    |

| Channel overlap ratio - two-sided                     | 0.20                                                                                  |

| Spacer width (nm)                                     | 5                                                                                     |

| Spacer k value                                        | 3.0                                                                                   |

| Contact CD (nm) - finFET, LGAA                        | 20                                                                                    |

| Device architecture key ground rules                  |                                                                                       |

| Device lateral pitch (nm)                             | 24                                                                                    |

| Device height (nm)                                    | 67                                                                                    |

| FinFET Fin width (nm)                                 |                                                                                       |

| Footprint drive efficiency - finFET                   |                                                                                       |

| Lateral GAA vertical pitch (nm)                       | 17.0                                                                                  |

| Lateral GAA (nanosheet) thickness (nm)                | 6.0                                                                                   |

| Number of vertically stacked nanosheets on one device | 4                                                                                     |

| LGAA width (nm) - HP                                  | 20                                                                                    |

| LGAA width (nm) - HD                                  | 10                                                                                    |

| LGAA width (nm) - SRAM                                | 6                                                                                     |

| Footprint drive efficiency - lateral GAA - HP         | 5.47                                                                                  |

| Device effective width (nm) - HP                      | 208.0                                                                                 |

| Device effective width (nm) - HD                      | 128.0                                                                                 |

| PN separation width (nm)                              | 30                                                                                    |

| PN separation vertical space (nm)                     |                                                                                       |

圖（五）為 1.5 奈米技術節點的 Device Architecture and Ground Rules Roadmap for Logic Devices

【擷取自 IRDS Roadmap 2023 Device Ground Rules】

| YEAR OF PRODUCTION                                    | 2028                                                                                |

|-------------------------------------------------------|-------------------------------------------------------------------------------------|

| <i>Logic industry "Node Range" Labeling</i>           | <b>2028-LGAA</b>                                                                    |

| <i>Fine-pitch 3D integration scheme</i>               | <b>G42M16</b>                                                                       |

| <i>Logic device structure options</i>                 | <b>"1.5nm"</b>                                                                      |

| <i>Backside structure options</i>                     | <b>Stacking</b>                                                                     |

| <i>Platform device for logic</i>                      | <b>LGAA</b>                                                                         |

|                                                       |  |

| <b>LOGIC DEVICE ELECTRICAL SPECS</b>                  |                                                                                     |

| Power Supply Voltage - Vdd (V)                        | <b>0.60</b>                                                                         |

| Subthreshold slope (mV/dec) - HP (mV/dec)             | <b>70</b>                                                                           |

| Subthreshold slope (mV/dec) - HD (mV/dec)             | <b>67</b>                                                                           |

| Capacitive equivalent thickness (CET) (nm) [2]        | <b>0.90</b>                                                                         |

| Vt,sat at Ioff=10nA/um - HP (mV)                      | <b>164</b>                                                                          |

| Vt,sat (mV) at Ioff=100pA/um - HD (mV) [3][4]         | <b>276</b>                                                                          |

| Effective mobility (cm <sup>2</sup> /V.s.)            | <b>80</b>                                                                           |

| Rsd (Ohms.um) [5]                                     | <b>245</b>                                                                          |

| Ballistic Injection velocity (cm/s)                   | <b>9.00E+06</b>                                                                     |

| Vdsat (V) - HP                                        | <b>0.108</b>                                                                        |

| Vdsat (V) - HD                                        | <b>0.108</b>                                                                        |

| Ion (uA/um) at Ioff=10nA/um - HP [6]                  | <b>759</b>                                                                          |

| Ion (uA/device) at Ioff=10nA/um - HP [7]              | <b>158</b>                                                                          |

| Ion (uA/um) at Ioff=100pA/um - HD [8]                 | <b>546</b>                                                                          |

| Ion (uA/device) at Ioff=100pA/um - HD [9]             | <b>114</b>                                                                          |

| Cch,total (fF/um <sup>2</sup> ) - HP/HD [8]           | <b>38.35</b>                                                                        |

| Gate height over fin (nm)                             | <b>10</b>                                                                           |

| Cch (fF/um) - HP [8]                                  | <b>0.37</b>                                                                         |

| Cch (fF/um) - HD [8]                                  | <b>0.37</b>                                                                         |

| CV/I (ps) - FO3 load, HP [9]                          | <b>0.87</b>                                                                         |

| I/(CV) (1/ps) - FO3 load, HP [10]                     | <b>1.15</b>                                                                         |

| Energy per switching (CV2) (fJ/switch) - FO3 load, HP | <b>0.40</b>                                                                         |

圖（六） 1.5 奈米技術節點的 Projected Electrical Specifications of Logic Core Device

【擷取自 IRDS Roadmap 2023 Device Ground Rules】

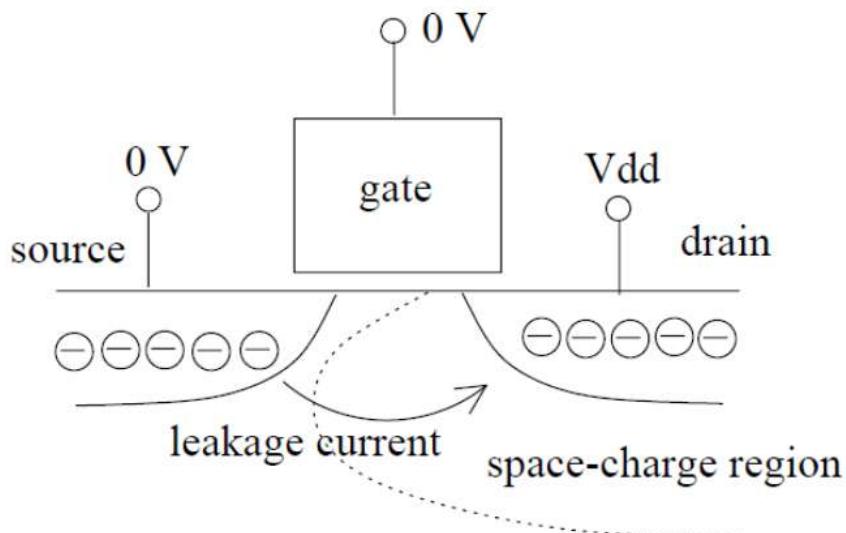

## （二）電晶體背景知識

1. 環繞式閘極（Gate-All-Around, GAA）技術：GAA 是電晶體技術的一項重要創新，其核心設計特點是通道被閘極材料完全包覆，實現了對通道的全方位控制。這一結構相較於 FinFET，有以下技術優勢：

- (1) 更高的電流控制能力：閘極對通道的完全包覆減少了漏電流，提升了訊號穩定性。

- (2) 更低的功耗：由於通道控制效率提升，GAA 技術可在更低的工作電壓下實現高效運作。

(3) 更好的短通道效應控制：短通道效應是隨著技術節點縮小而產生的漏電問題，GAA 技術通過全方位包覆結構，有效抑制了這一現象。

## 2. 關鍵技術名詞解釋：

- (1) 有效寬度 (Weff)：Weff 代表電晶體通道的有效導電寬度，與驅動能力直接相關。較高的 Weff 其元件的電流輸出能力越高。

- (2) 寄生電容 (Ceef)：Ceef 是指電晶體運作中由結構特性產生的多餘電容，會增加功耗並降低開關速度。透過優化 GAA 通道設計，可有效降低寄生電容，從而實現更好的性能與功耗平衡。

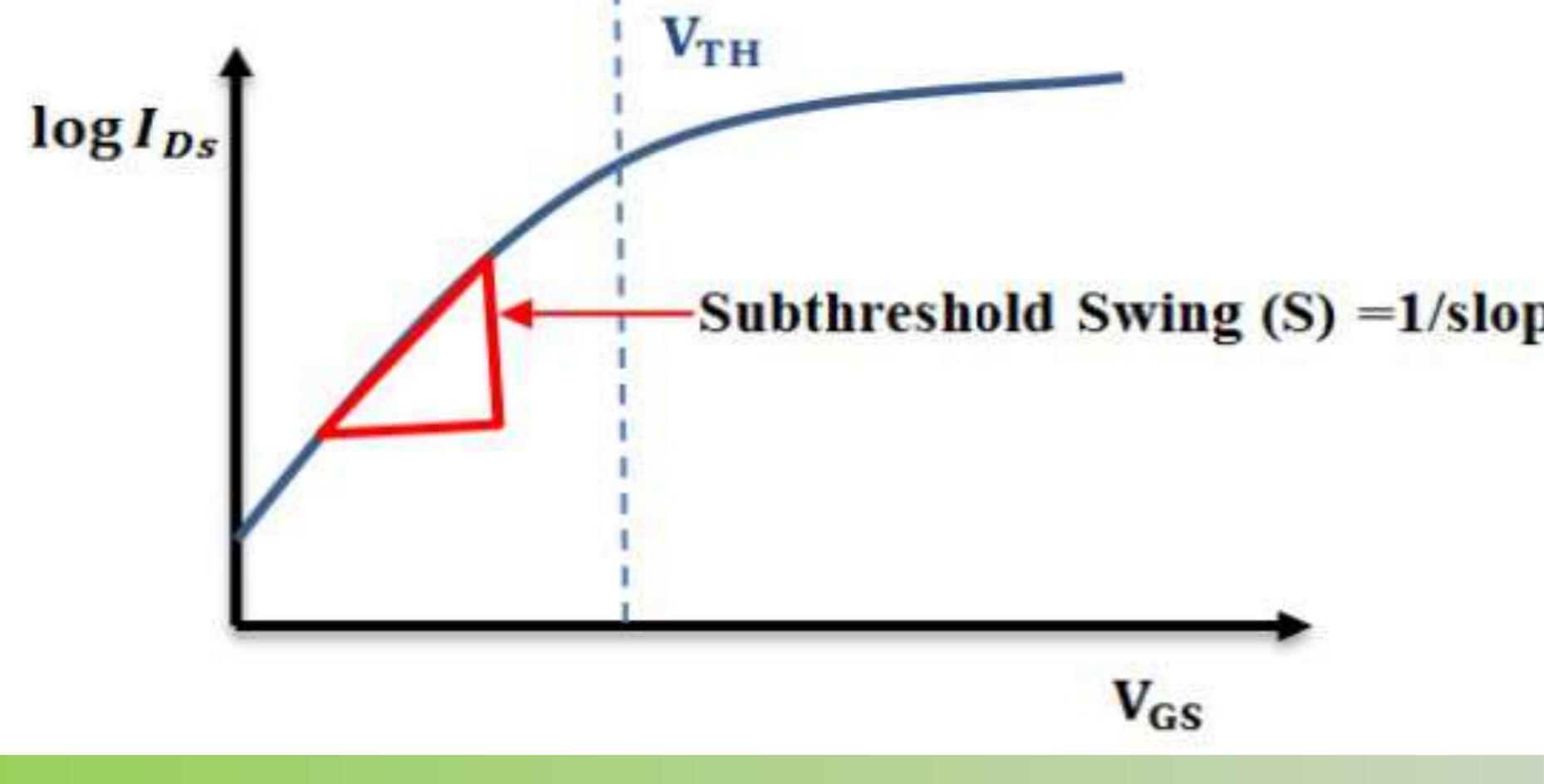

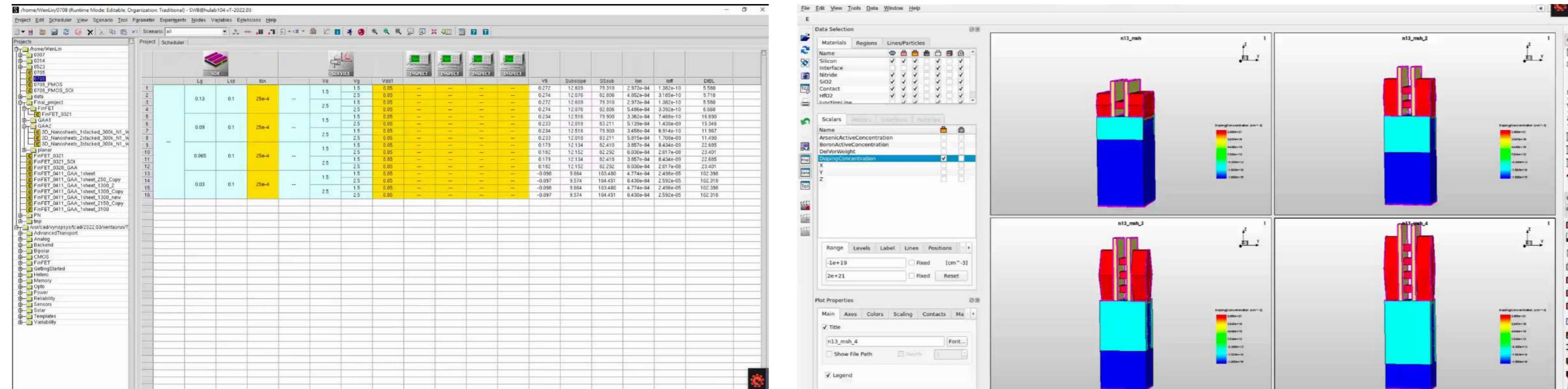

- (3) 次臨界擺幅 (Subthreshold Swing, SS)：SS 是衡量電晶體在次臨界區間的開關效率的重要指標，值越小代表開關速度越快。研究顯示，GAA 奈米片結構在 5 nm 節點的 SS 僅為 75~85 mV/dec，表現優於 3nm 主流量產元件 FinFET。

- (4) 短通道效應 (Short Channel Effects, SCE)：短通道效應是當電晶體通道縮短時，汲極的電位影響通道內電子傳輸，導致漏電流增加的現象。GAA 技術通過環繞式包覆的設計，成功減少了短通道效應，特別是在 2 nm 及以下技術節點中尤為關鍵。

圖（七）為短通道效應示意圖。

【圖片引用自 Kumar (2016)】

(5) 本質延遲 (Intrinsic Delay)：本質延遲是衡量電晶體開關速度的重要指標，與驅動電流 ( $I_{eff}$ ) 及等效電容 ( $C_{eff}$ ) 密切相關。其表現可由公式  $\tau = \frac{C_{eff} \times V_{DD}}{I_{eff}}$  描述，其中  $C_{eff}$  為等效電容； $I_{eff}$  為有效驅動電流； $V_{DD}$  為工作電壓，表示充放電時間受通道電容與驅動能力影響。

## 貳、研究設備與器材

## 一、軟體介紹：

### (一) Sentaurus TCAD :

1. 本研究採用的模擬工具 Sentaurus TCAD，為國際大廠如 TSMC、Intel、Samsung、IMEC 等實際使用於先進製程開發（如 GAAFET、CFET）的主流模擬平台。由於其完整支援次奈米尺度所需之量子效應、載子統計、摻雜分布、接觸物理模型等複雜交互現象，因此為目前少數能夠模擬真實奈米尺度元件行為的商用軟體。在產業與學界均具高度認可。

2. 多項關鍵論文（Loubet et al., 2017；Ha et al., 2022）皆使用 TCAD 模擬奈米尺度 GAAFET 結構，驗證其電性趨勢，並與實際元件製程進行比對。顯示 TCAD 模擬在先進元件開發中具備高度準確性與產業實用性。

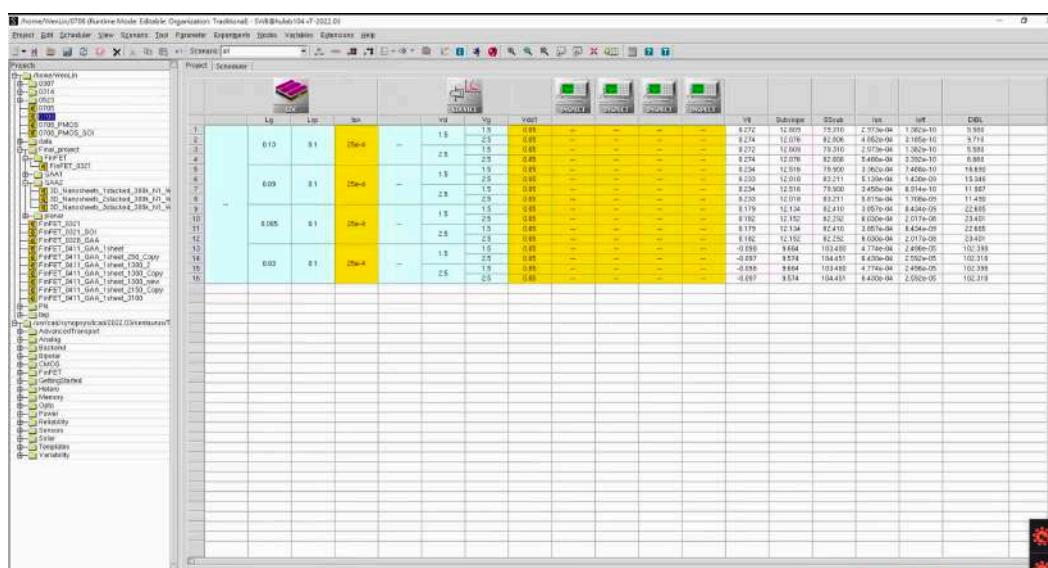

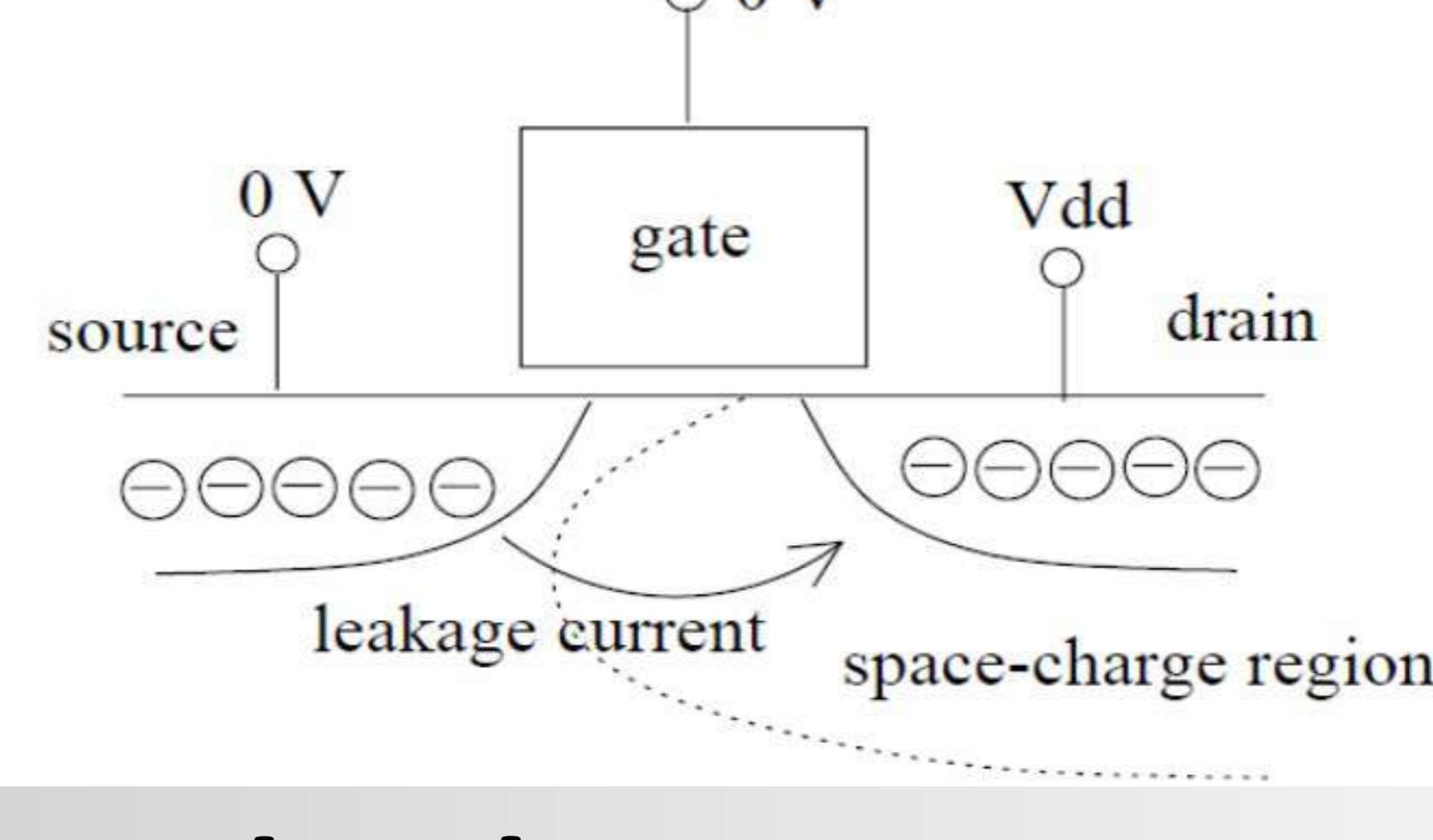

圖（八）Sentaurus TCAD 介面。【擷取自 Sentaurus TCAD】

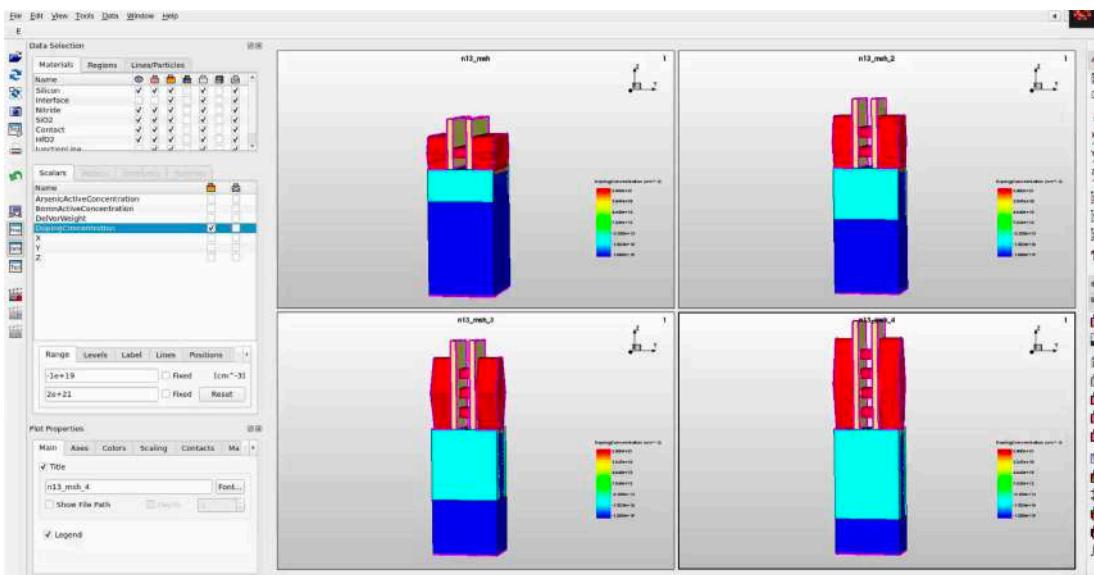

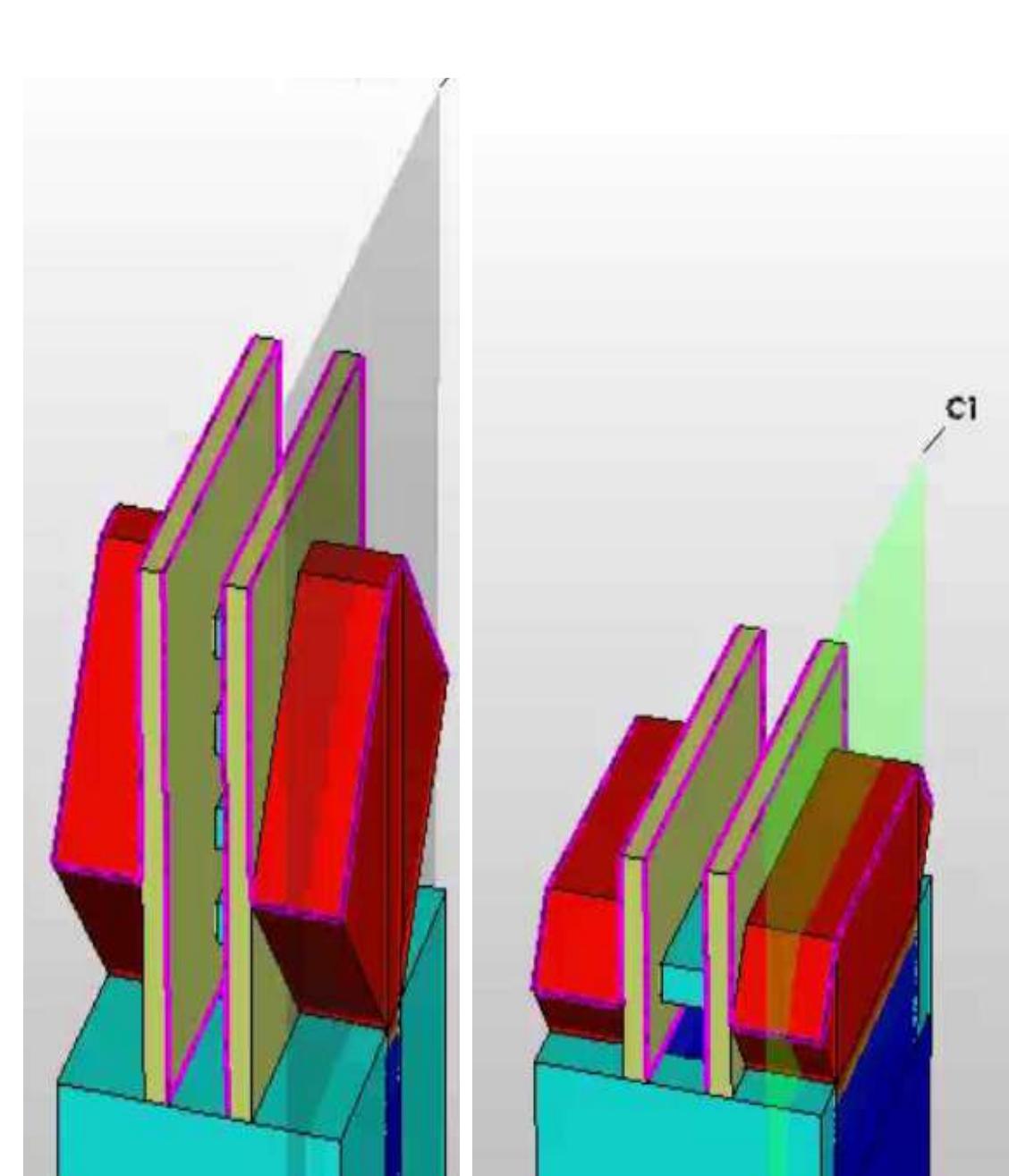

圖（九）Sentaurus TCAD 介面，顯示不同通道數量之三維 NSFET 結構。

【擷取自 Sentaurus TCAD】

## 參、研究過程或方法

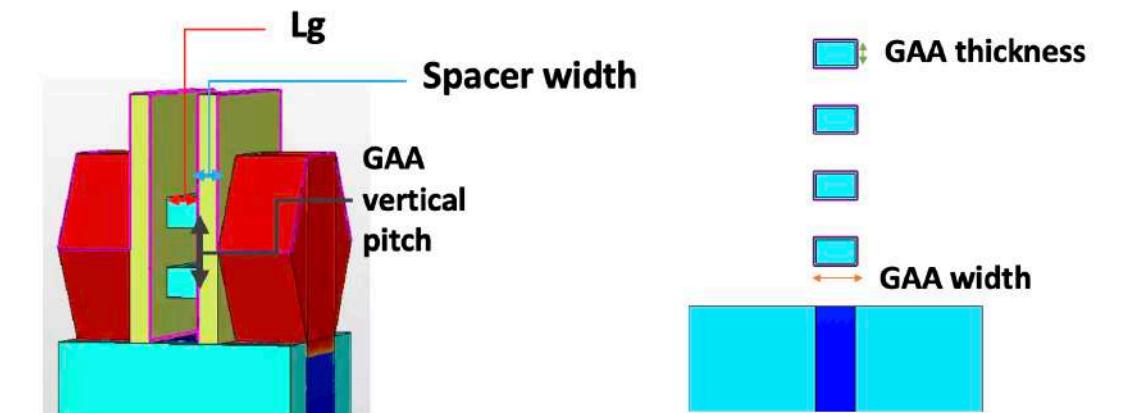

一、對照 IRDS Roadmap 2023 Device Ground Rules 找出側壁寬度（Spacer width）、閘極長度（Gate length）、環繞式閘極垂直間距（GAA vertical pitch）、環繞式閘極厚度（GAA thickness）、環繞式閘極寬度（GAA width）之參數。

圖（十）為設計之 NSFET 結構圖，標示各參數在 3D 結構與剖面中的對應位置。

【擷取自 Sentaurus TCAD 模擬結果，並以 Microsoft PowerPoint 軟體標註】

二、使用 Sentaurus Structure Editor (SDE) 程式碼依參數建立結構，參考上圖

(十)。

三、使用 TCAD 軟體之 Sentaurus Device (SDevice) 模組進行電性模擬，包含偏壓掃描與物理解釋。並採用以下偏壓條件：

(一)  $V_{ds} = 0.6$  V (高電壓區)

(二)  $V_{ds} = 0.05$  V (近線性區)

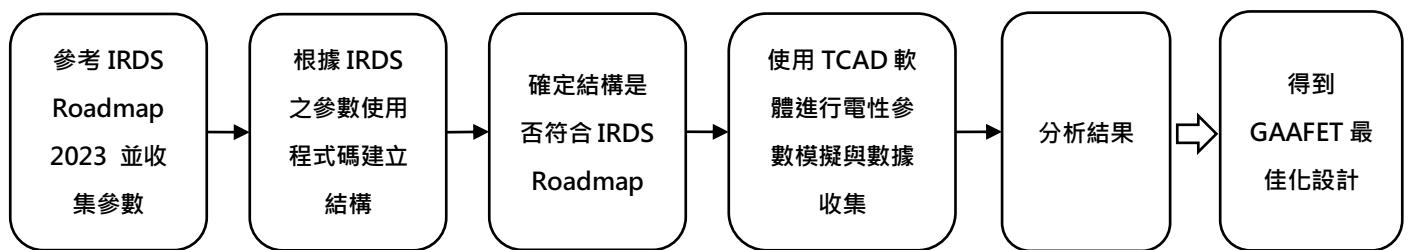

圖（十一）研究流程圖。【使用 Microsoft PowerPoint 軟體繪製】

四、收集各項數值並比較次臨界擺幅 (SS) 、臨界電壓 ( $V_t$ ) 、導通電流 ( $I_{on}$ ) 、關斷電流 ( $I_{off}$ ) 、汲極偏壓導致通道能障降低效應 (DIBL) 、有效電流 ( $I_{eff}$ ) 、有效電容 ( $C_{eff}$ ) 、本質延遲 (Intrinsic Delay) 時間。

## 肆、 研究結果

### 一、 GAAFET Parameters

表（一）根據 IRDS Roadmap 提取的所需參數

|                                      |           |    |    |    |

|--------------------------------------|-----------|----|----|----|

| 閘極長度 (nm)                            | 12        |    |    |    |

| 奈米片層數                                | 1         | 2  | 3  | 4  |

| 奈米片厚度 (nm)                           | 6         |    |    |    |

| 奈米片垂直間距 (nm)                         | 17        |    |    |    |

| 奈米片寬度 (nm)                           | 58        | 26 | 15 | 10 |

| 奈米片等效寬度 (nm)                         | 128       |    |    |    |

| 等效氧化物厚度 (nm)                         | 0.7       |    |    |    |

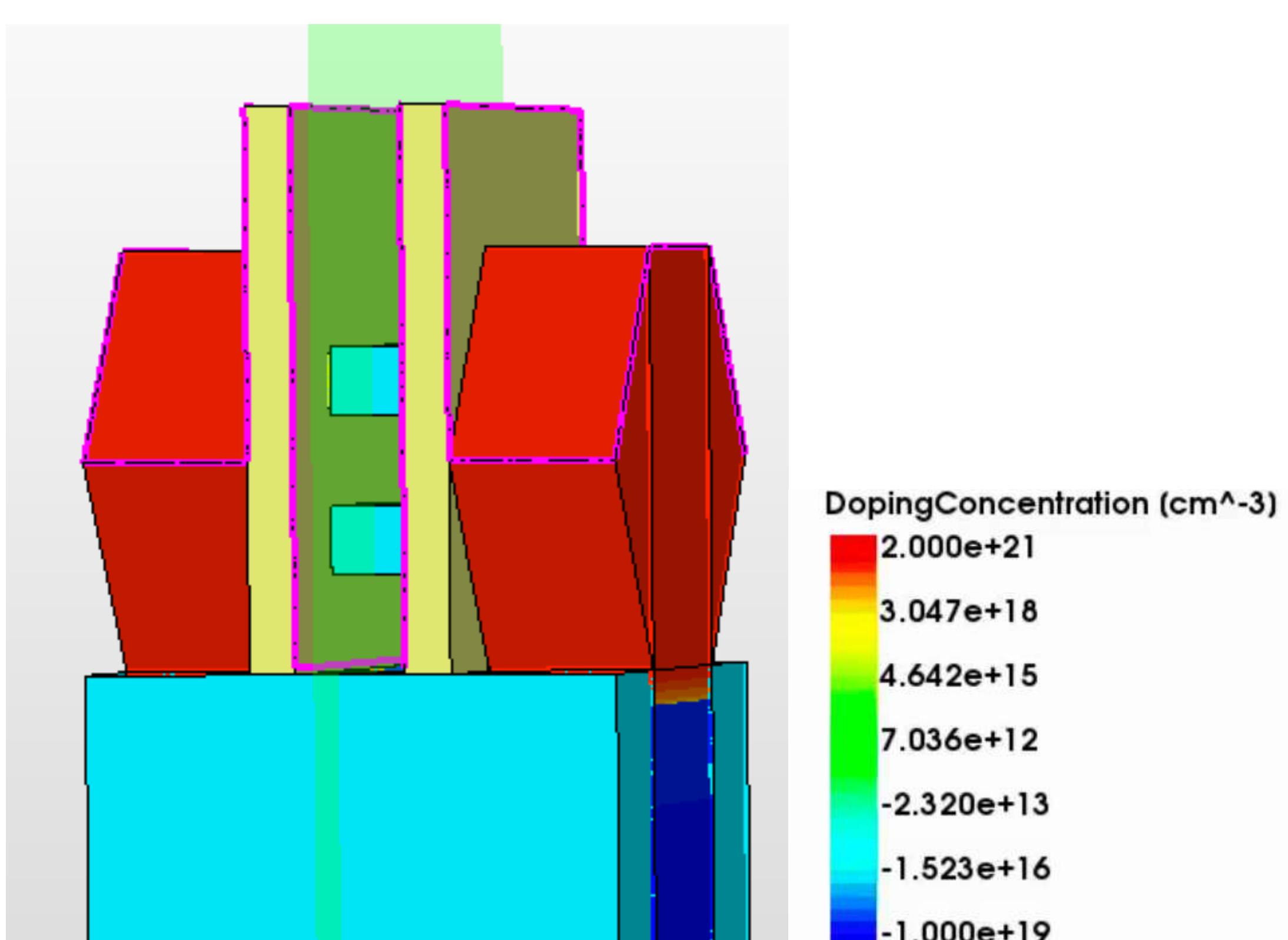

| 通道摻雜濃度 ( $\text{cm}^{-3}$ ) (硼摻雜)    | $10^{16}$ |    |    |    |

| 汲極/源極摻雜濃度 ( $\text{cm}^{-3}$ ) (砷摻雜) | $10^{21}$ |    |    |    |

| 基板摻雜濃度 ( $\text{cm}^{-3}$ ) (硼摻雜)    | $10^{19}$ |    |    |    |

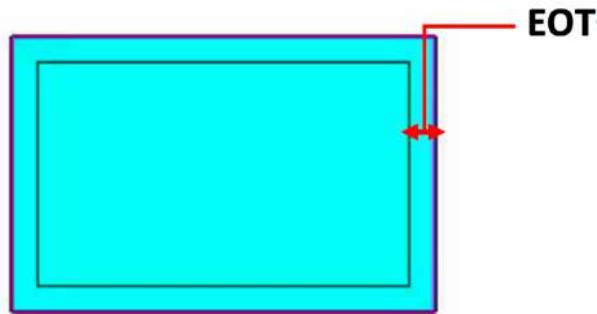

圖（十二）NSFET 剖面圖與 EOT 位置參考圖。

【擷取自 Sentaurus TCAD 模擬結果，並以 Microsoft PowerPoint 軟體標註】

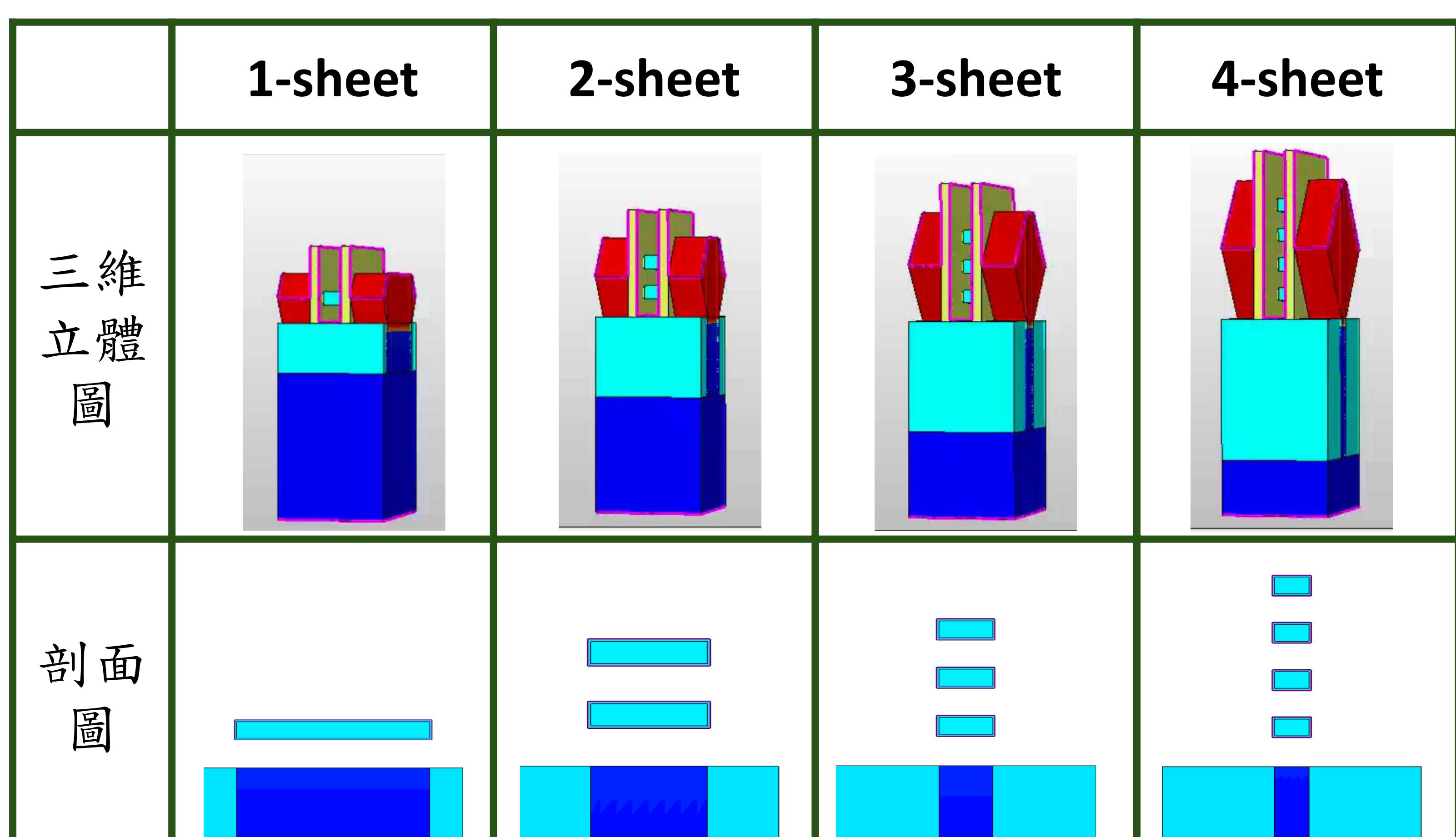

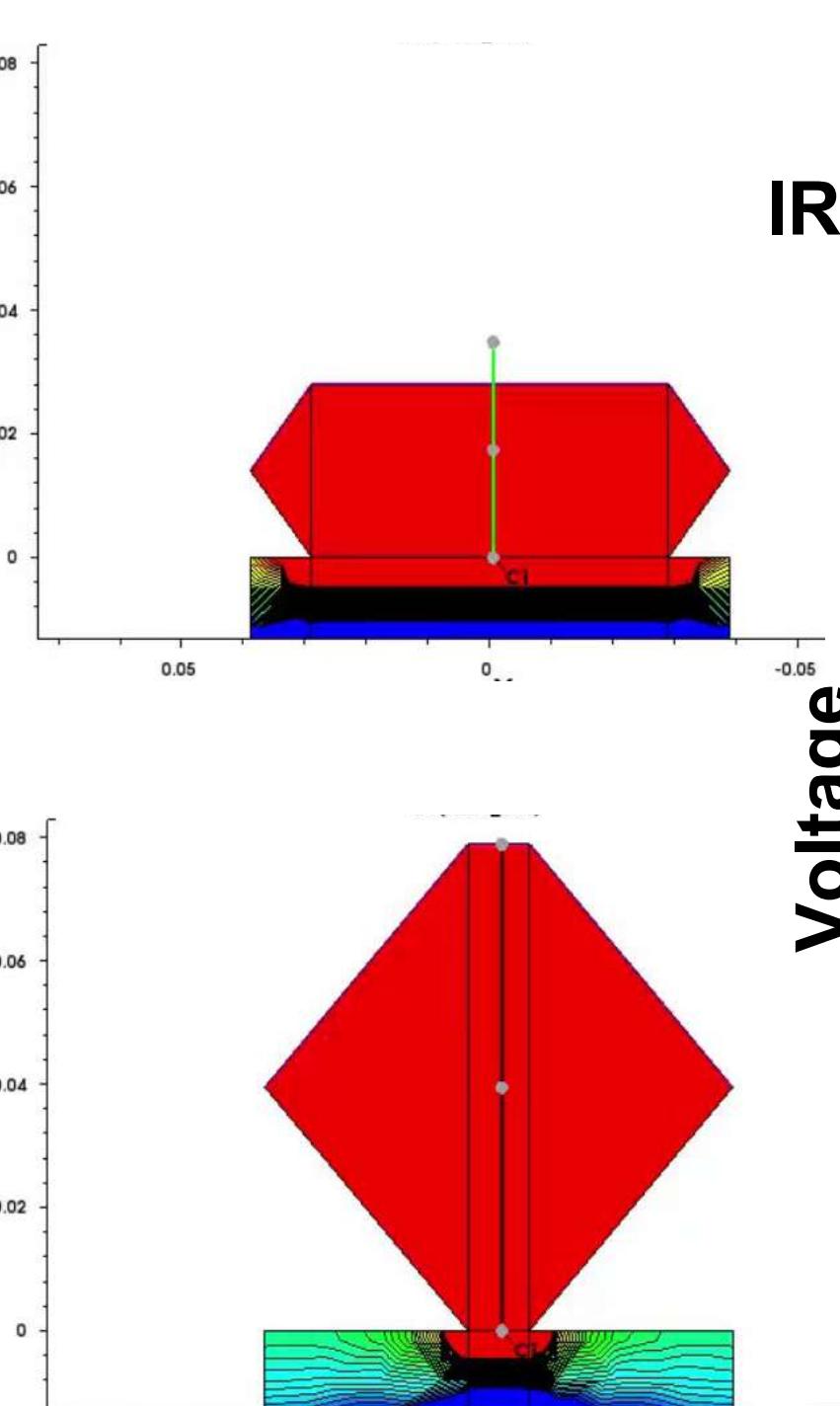

## 二、不同奈米片數 GAAFET 之結構

|              | 1-sheet | 2-sheet | 3-sheet | 4-sheet |

|--------------|---------|---------|---------|---------|

| 三維立體圖        |         |         |         |         |

| 下圖中綠色剖面下之剖面圖 |         |         |         |         |

表（二）模擬結果之三維立體圖與剖面圖

【擷取自 Sentaurus TCAD 模擬結果】

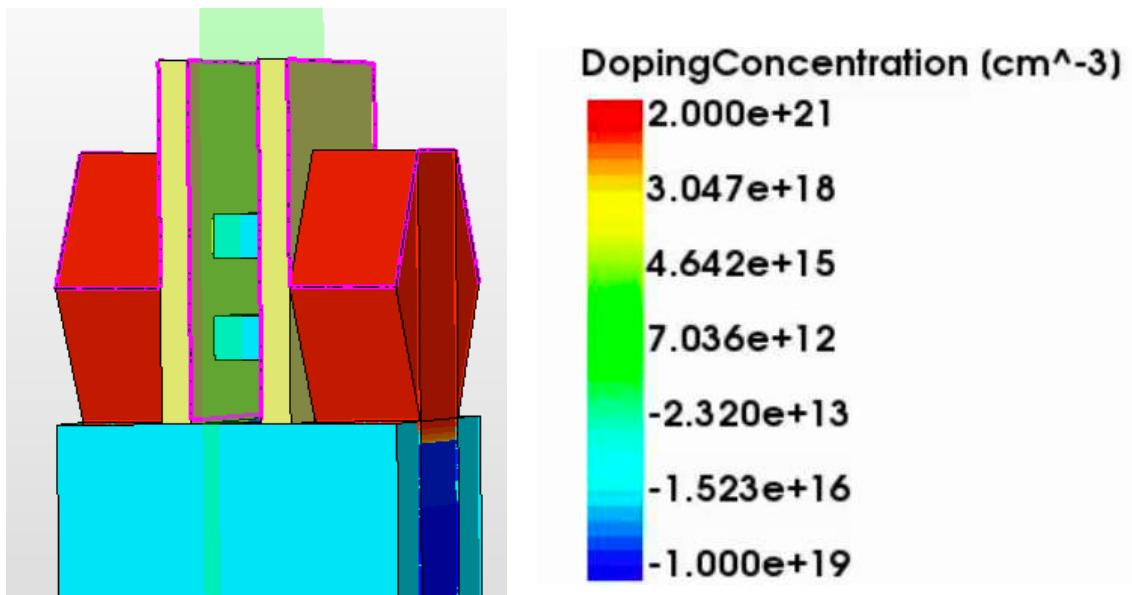

圖（十三）三維 NSFET 結構示意圖與摻雜濃度（Doping Concentration）N-type 砷摻雜為正值 P-type 硼摻雜為負值。【擷取自 Sentaurus TCAD 模擬結果】

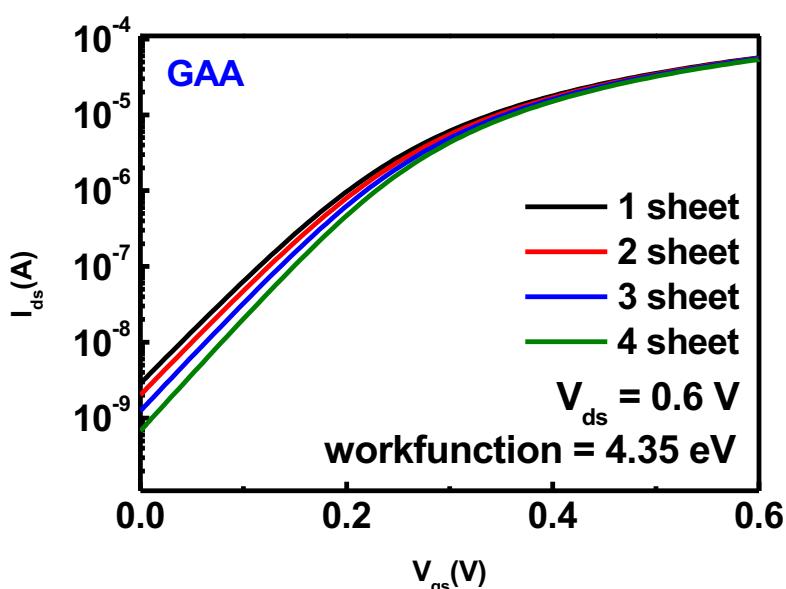

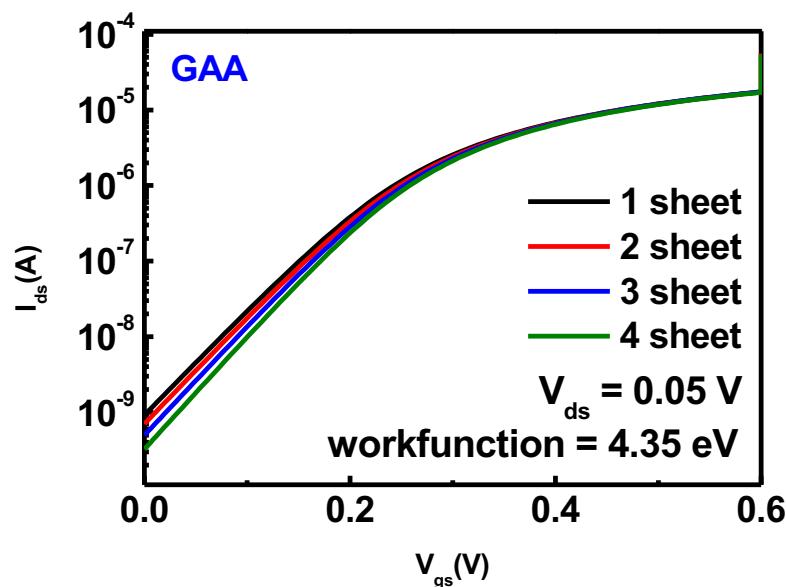

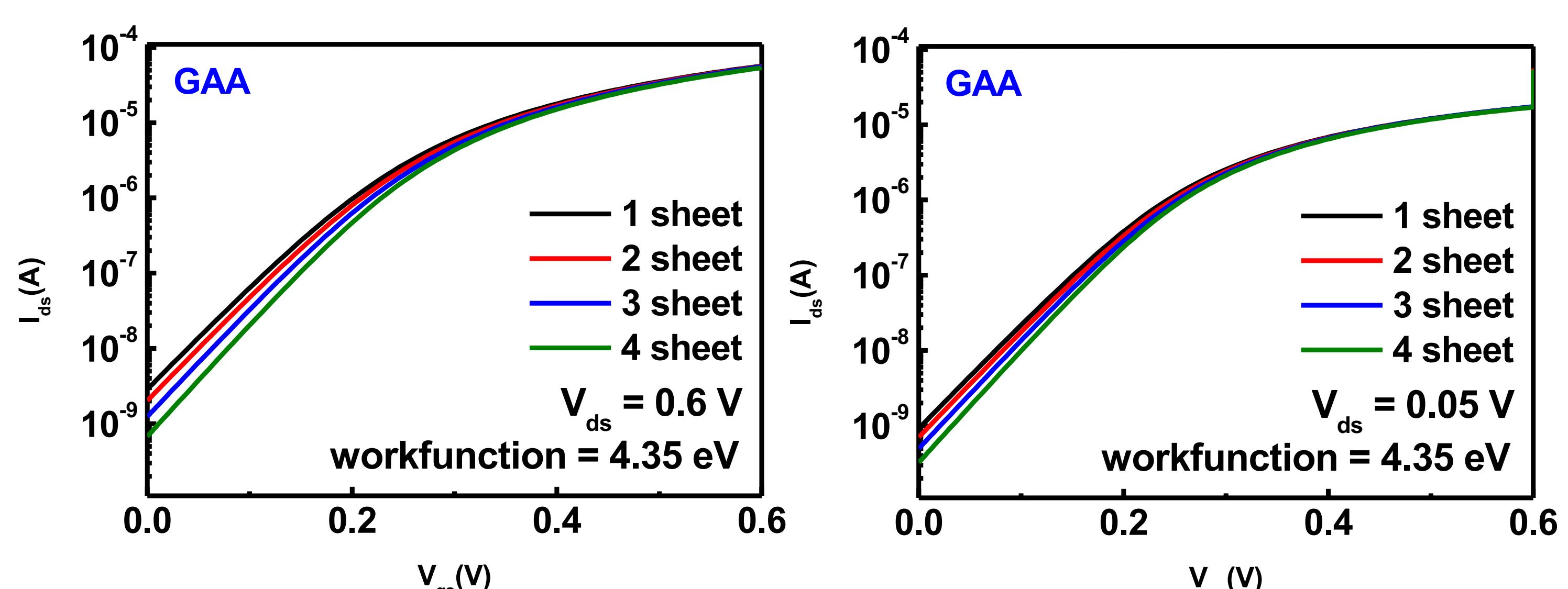

### 三、 $I_{ds}$ - $V_{gs}$ 電流電壓特性圖

（一）展示各結構在較高汲極電壓下的電流變化，比較開關特性與短通道效應的抑制效果。

圖（十四）不同奈米片層數 GAAFET 在  $V_{ds} = 0.6$  V 下的  $I_{ds}$ - $V_{gs}$  曲線。

【收集 Sentaurus TCAD 模擬結果，並使用 Origin 軟體繪製成表格】

(二) 展示各結構在低汲極電壓下的導通與關斷特性，反映元件在近線性區的電流特性。

圖（十五）不同奈米片層數 GAAFET 在  $V_{ds} = 0.05 \text{ V}$  下的  $I_{ds}$ - $V_{gs}$  曲線。

【收集 Sentaurus TCAD 模擬結果，並使用 Origin 軟體繪製成表格】

#### 四、不同奈米片層數下電性參數模擬數據

##### (一) $I_{ds}$ - $V_{gs}$ Curves

表 (三) 不同奈米片層數 (1-4 sheet) GAAFET 模擬結果

|                      | 1-sheet | 2-sheet | 3-sheet | 4-sheet |

|----------------------|---------|---------|---------|---------|

| $I_{on}$ ( $\mu A$ ) | 56.83   | 55.91   | 55.41   | 55.38   |

| DIBL (mV/V)          | 76.588  | 70.595  | 63.159  | 54.514  |

| SS (mV/dec)          | 79.954  | 78.811  | 77.055  | 74.768  |

| $V_{t,lin}$ (V)      | 0.246   | 0.251   | 0.256   | 0.261   |

| $I_{off}$ (nA)       | 2.871   | 2.025   | 1.247   | 0.680   |

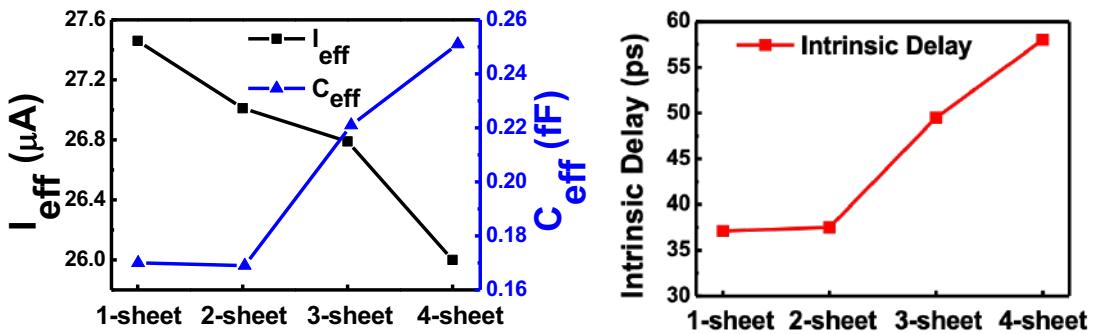

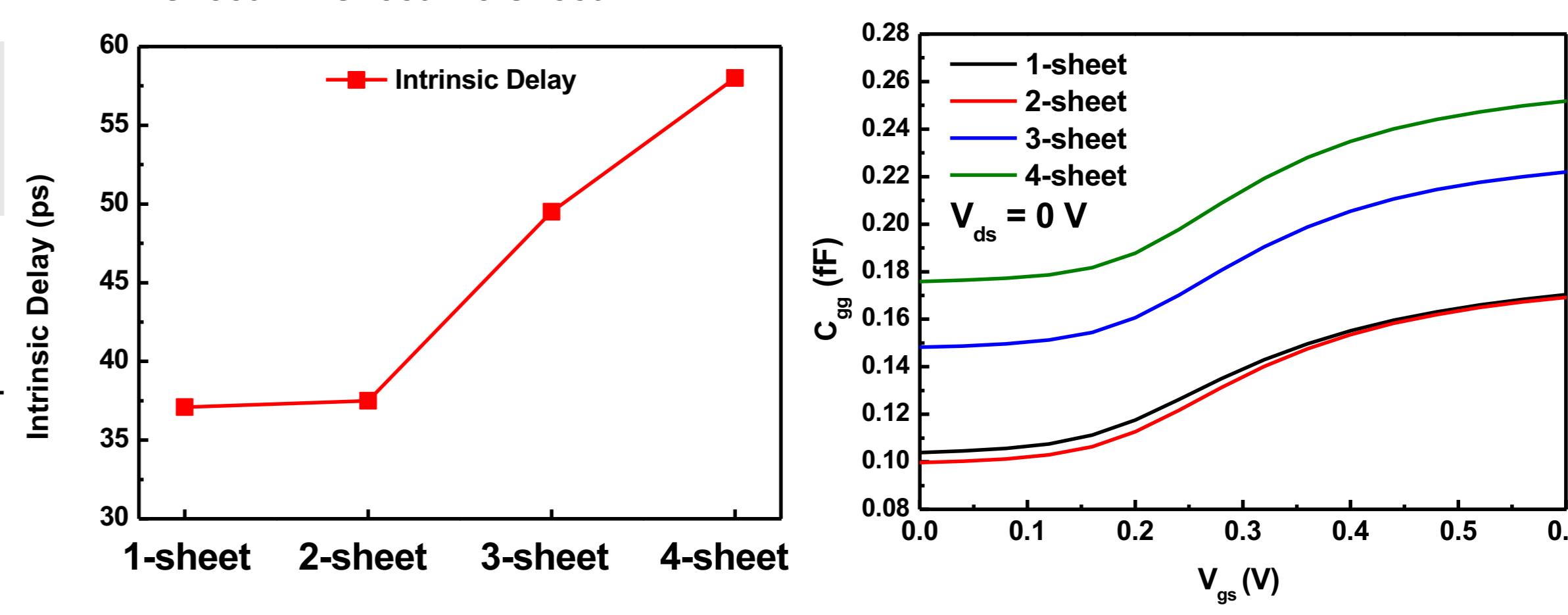

##### (二) 本質延遲 (Intrinsic Delay)

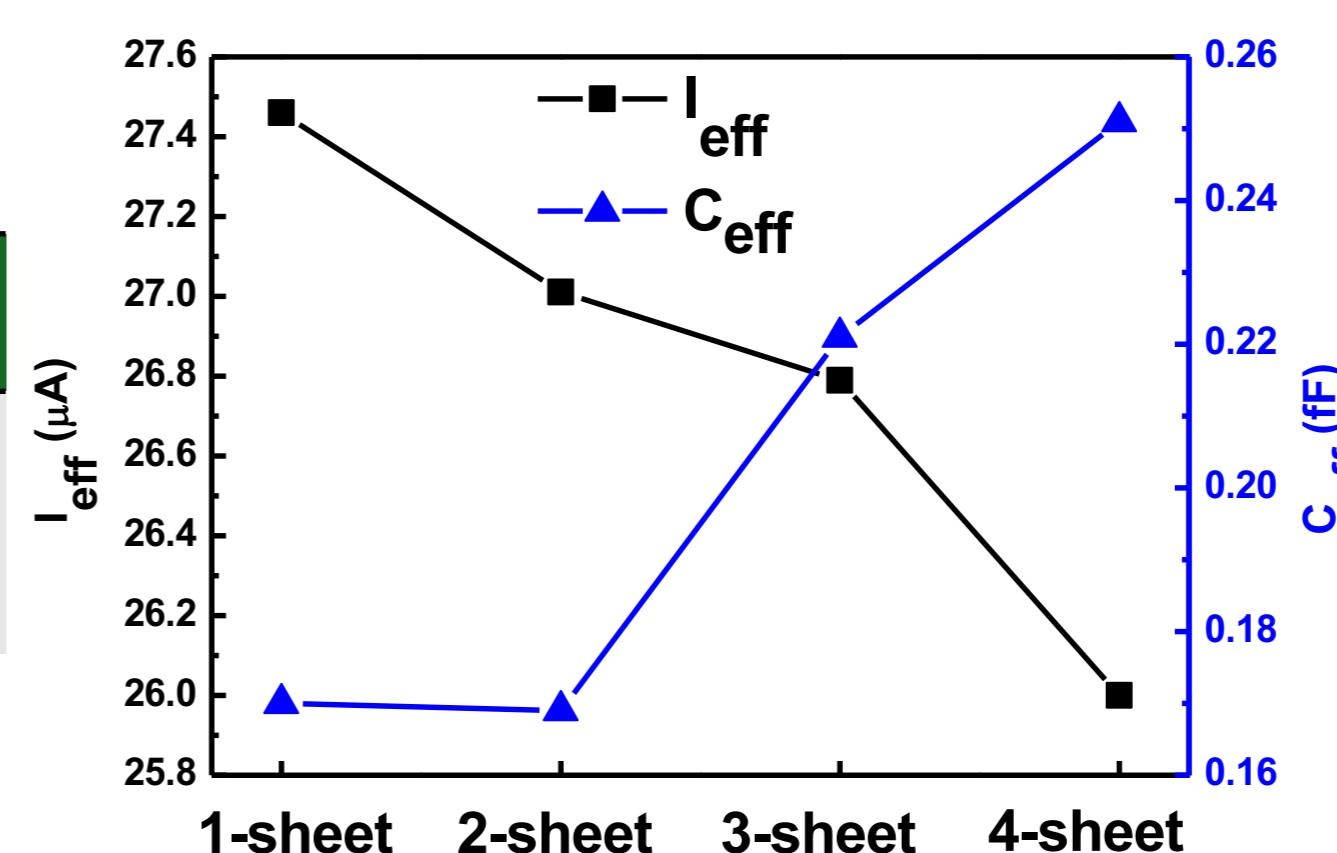

表 (四) 不同奈米片層數 (1-4 sheet) GAAFET 之  $I_{eff}$ 、 $C_{eff}$ 、Intrinsic Delay 與

源極/汲極磊晶面積比較

|                         | 1-sheet | 2-sheet | 3-sheet | 4-sheet |

|-------------------------|---------|---------|---------|---------|

| $I_{eff}$ ( $\mu A$ )   | 27.46   | 27.01   | 26.79   | 26.00   |

| $C_{eff}$ (fF)          | 0.170   | 0.169   | 0.221   | 0.251   |

| Intrinsic Delay<br>(ps) | 37.1    | 37.5    | 49.5    | 58.0    |

| 源極汲極磊晶<br>面積( $nm^2$ )  | 1902    | 1887    | 2312    | 2999    |

圖（十六）左圖為  $I_{eff}$  及  $C_{eff}$  變化圖；右圖為 Intrinsic Delay 變化圖

【收集 Sentaurus TCAD 模擬結果，並使用 Origin 軟體繪製成表格】

五、模擬結果顯示，各項電性參數隨奈米片數量的變化趨勢如下：

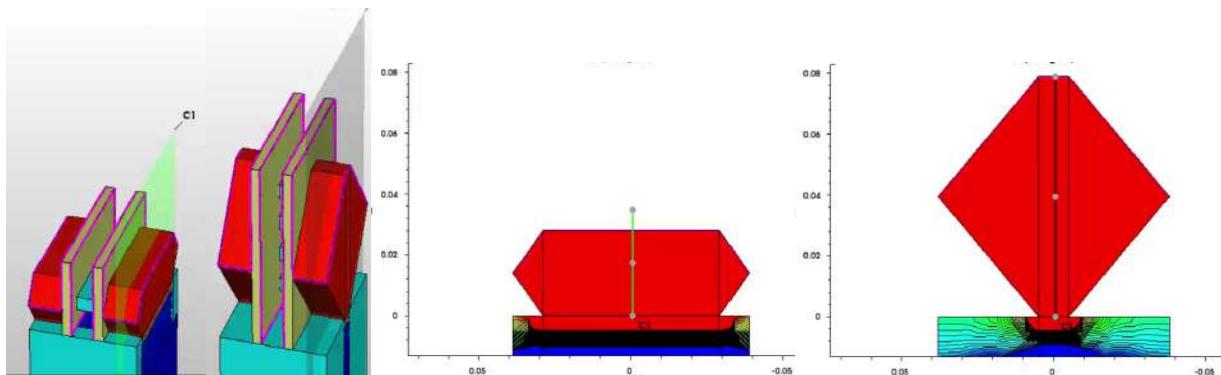

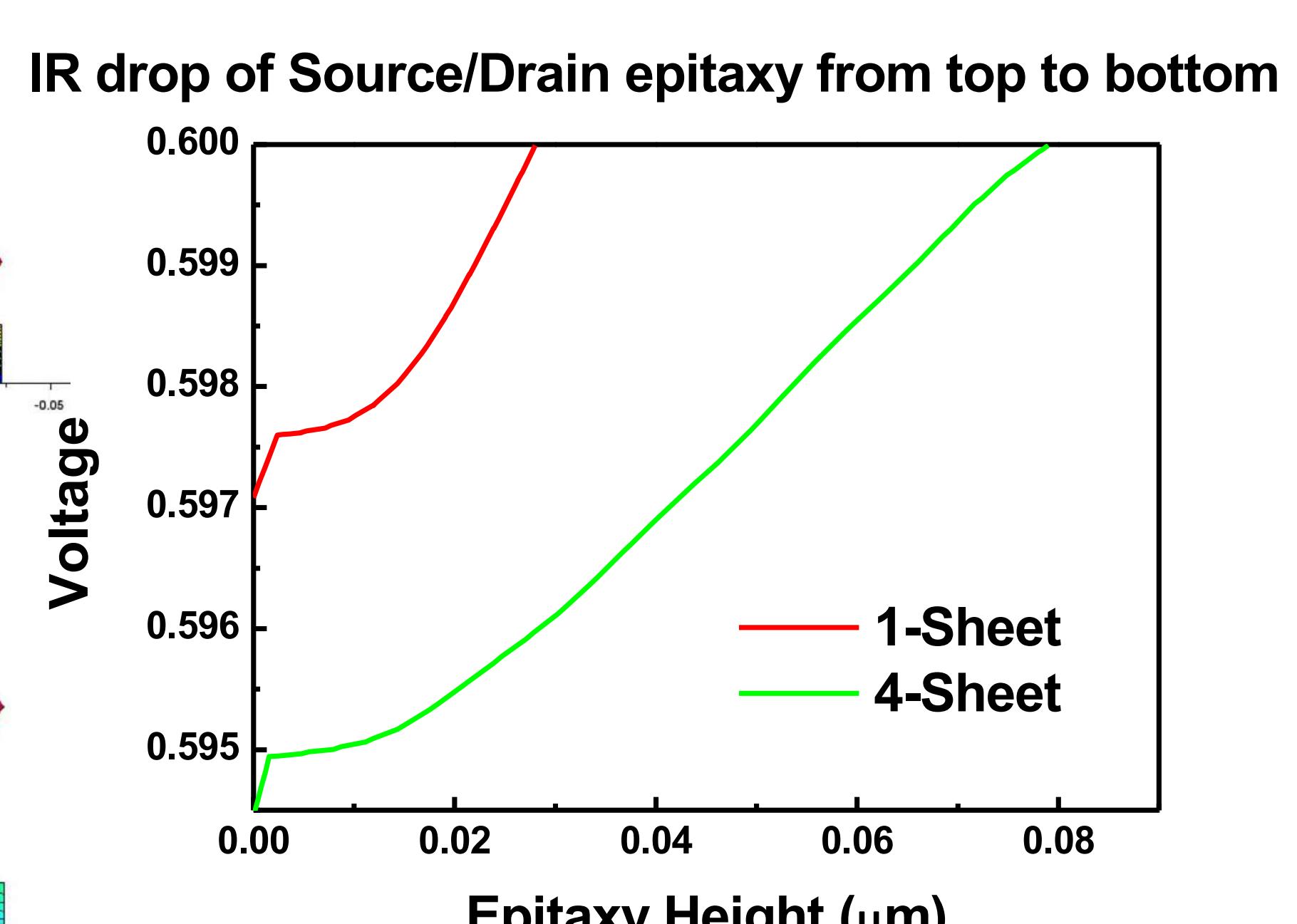

- (一) 導通電流 ( $I_{on}$ )：在高導通狀態下， $I_{on}$  數值在各結構間略有變動，在 55–57  $\mu A$  之間，而 1-sheet 結構的導通電流 ( $I_{on}$ ) 最高，數值達  $56.83 \mu A$ 。此差異原因如圖（十二）所示，1-sheet 結構的汲極磊晶高度較 4-sheet 結構低，其奈米片通道兩端之  $V_{ds}$  相較 4-sheet 較無損耗，因此擁有較高的導通電流。

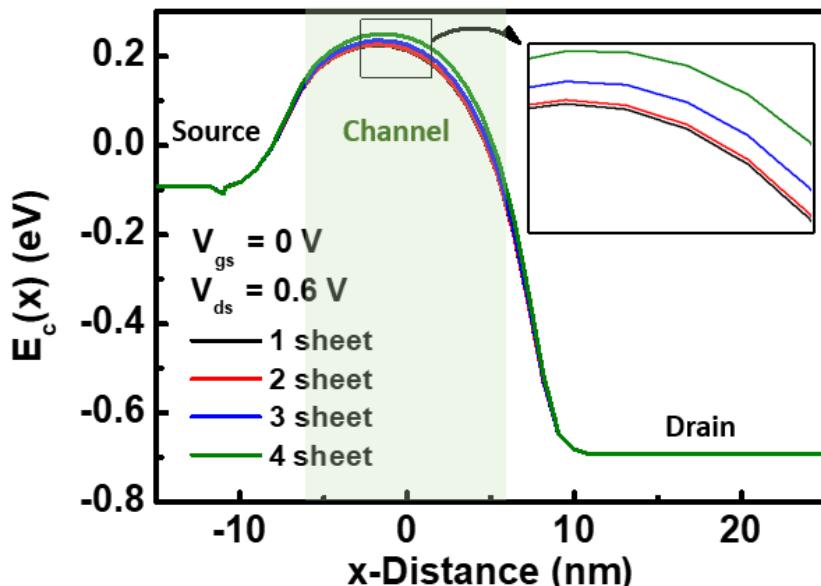

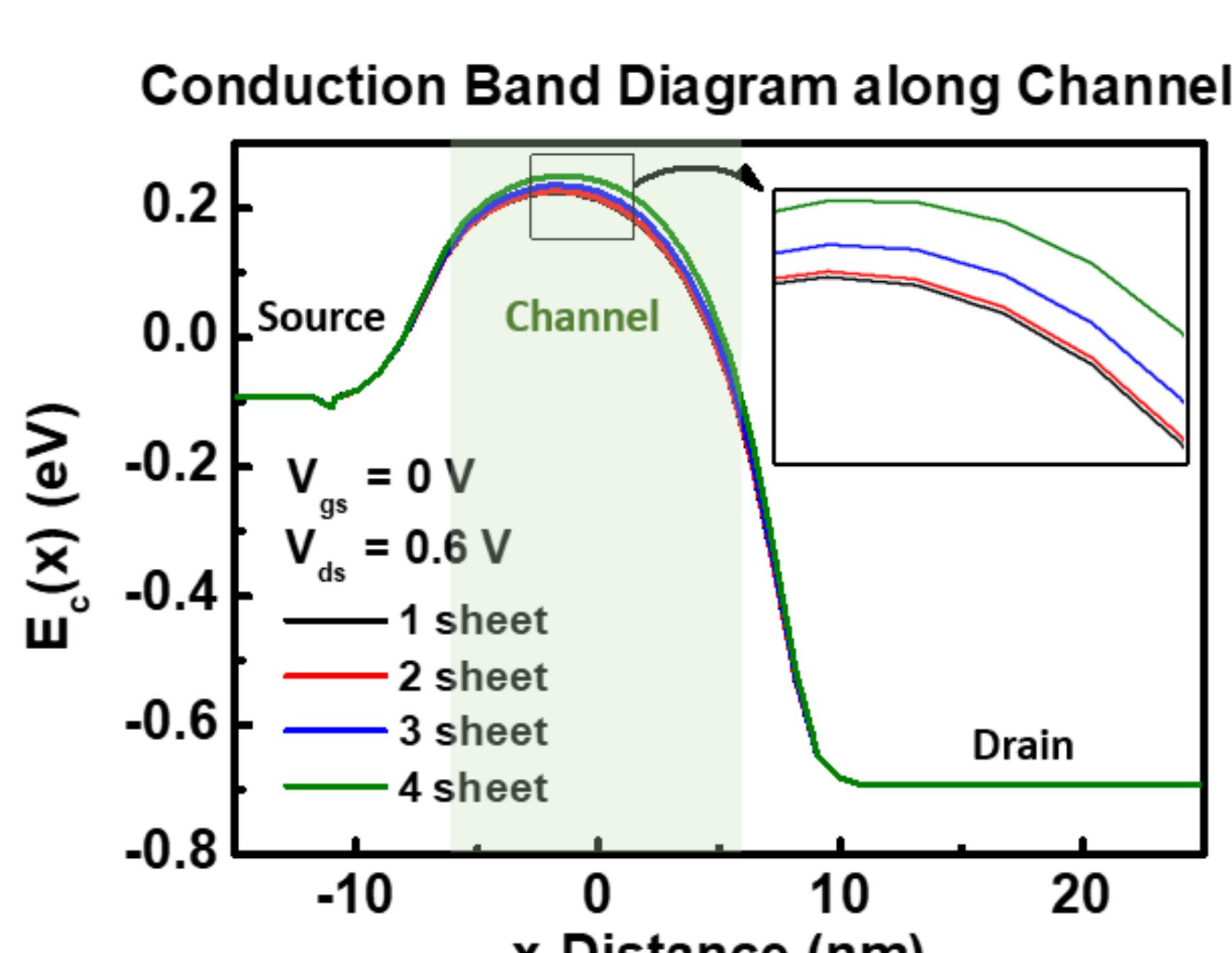

- (二) 汲極偏壓導致通道能障降低效應 (DIBL)：模擬數據顯示，DIBL 值亦隨奈米片層數增加而改善，從 1-sheet 的  $76.59 \text{ mV/V}$  降至 4-sheet 的  $49.18 \text{ mV/V}$ 。圖（十三）的導帶圖可看出 4-sheet 結構在關斷條件下相較 1,2,3-sheet 有更好的閘極對通道控制，因導帶受汲極電位下拉程度最小。證實較多的堆疊層能有效抑制短通道效應，提升元件在極小技術節點下的穩定性。

- (三) 次臨界擺幅 (SS)：隨著奈米片層數增加，SS 值由 1-sheet 的約  $79.95 \text{ mV/dec}$  逐步下降至 4-sheet 的  $74.77 \text{ mV/dec}$ 。這表示較多的奈米片層有助於提升閘極對通道的控制能力，從而改善開關效率與降低漏電效應。

- (四) 臨界電壓 ( $V_t$ )：模擬結果顯示，臨界電壓略有上升，從 1-sheet 的  $0.246 \text{ V}$  增加到 4-Sheet 的  $0.261$ 。反映隨著堆疊層數增加，4-sheet 元件較低的導通電流以及較小的次臨界擺幅，導致臨界電壓較高。

(五) 關斷電流 ( $I_{off}$ )： $I_{off}$  隨奈米片數增加明顯下降，從 1-sheet 的約 2.87 nA 降至 4-sheet 的 0.68 nA。此結果表明，增加堆疊層數而更好的閘極對通道控制，有助於顯著降低漏電流，提高元件的低功耗特性。

(六) 本質延遲 (Intrinsic Delay)：模擬結果顯示，本質延遲隨奈米片層數增加而上升，從 1-sheet 的 37.1 ps 增加至 4-sheet 的 58.0 ps。這一現象可歸因於兩個主要因素：

1. 有效驅動電流 ( $I_{eff}$ ) 下降：由於奈米片層數增加， $I_{eff}$  從 1-sheet 的 27.46  $\mu$ A 下降至 4-sheet 的 26.00  $\mu$ A。驅動電流的減少會影響元件的開關速度，使得開關時間變長，導致本質延遲增加。

2. 等效電容 ( $C_{eff}$ ) 增大：隨著奈米片層數增加， $C_{eff}$  亦從 1-sheet 的 0.170 fF 增加到 4-sheet 的 0.251 fF。這顯示較多的奈米片層會增加源極和汲極之間的電容耦合效應，使得充放電時間變長，進一步影響開關速度。

圖（十七） 1-sheet 與 4-sheet 結構在汲極磊晶剖面下的磊晶高度關係之比較。

【擷取自 Sentaurus TCAD 模擬結果】

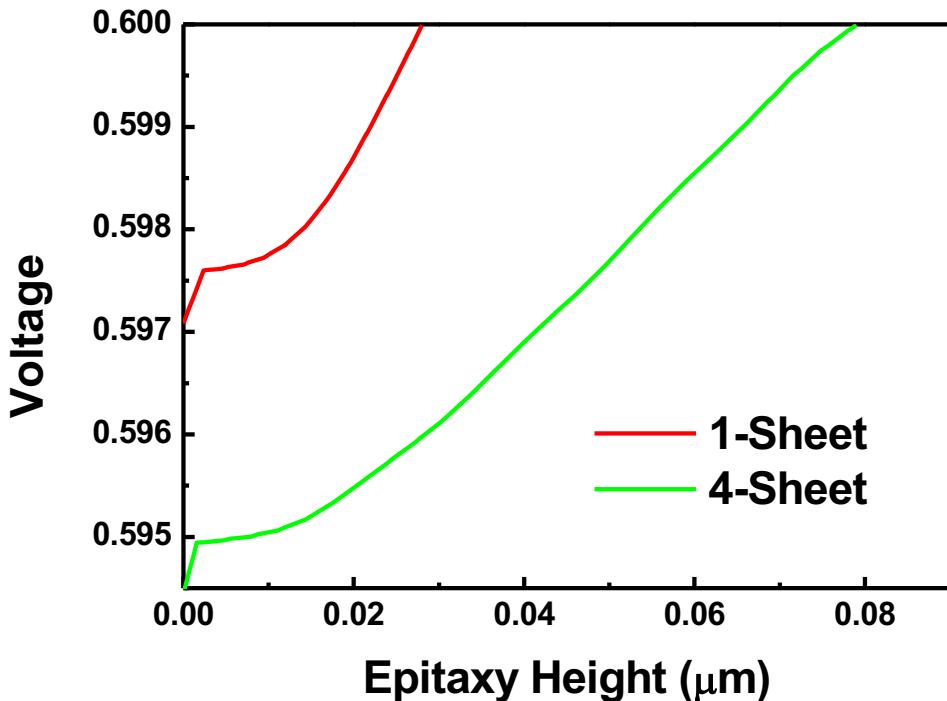

## IR drop of Source/Drain epitaxy from top to bottom

圖（十八）1-sheet 與 4-sheet 結構在汲極磊晶剖面下的電壓壓降關係圖。

【收集 Sentaurus TCAD 模擬結果，並使用 Origin 軟體繪製成表格】

## Conduction Band Diagram along Channel

圖（十九）關斷條件下，延通道方向的導帶圖（Conduction Band Diagram）。DIBL 效應可由圖中導帶被汲極電位往下影響程度得知：4-sheet 結構通道部分導帶受汲極下拉程度較少，代表閘極有較好的控制能力。

【收集 Sentaurus TCAD 模擬結果，並使用 Origin 軟體繪製成表格】

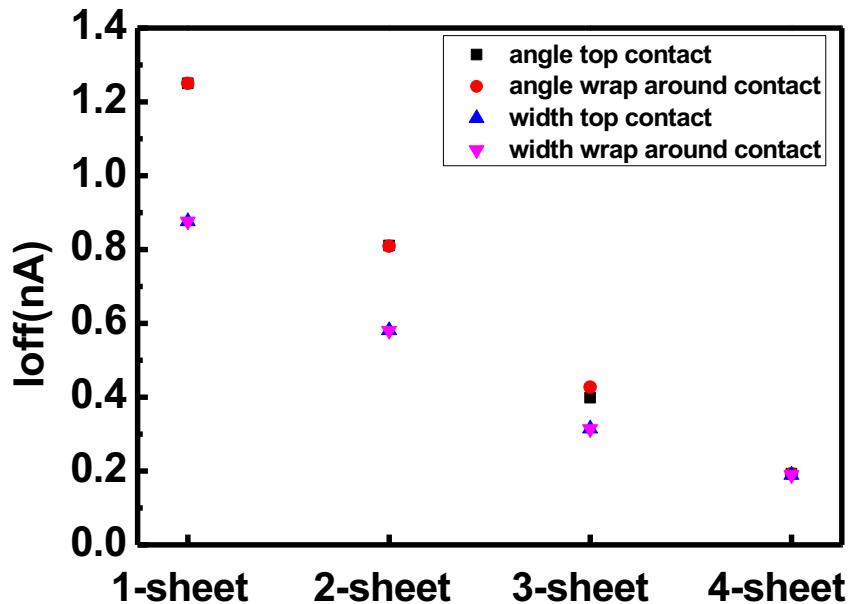

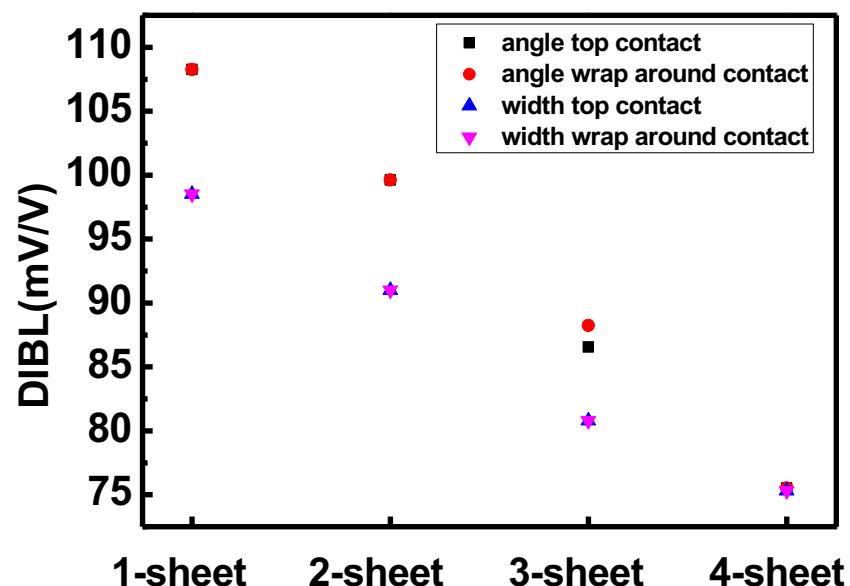

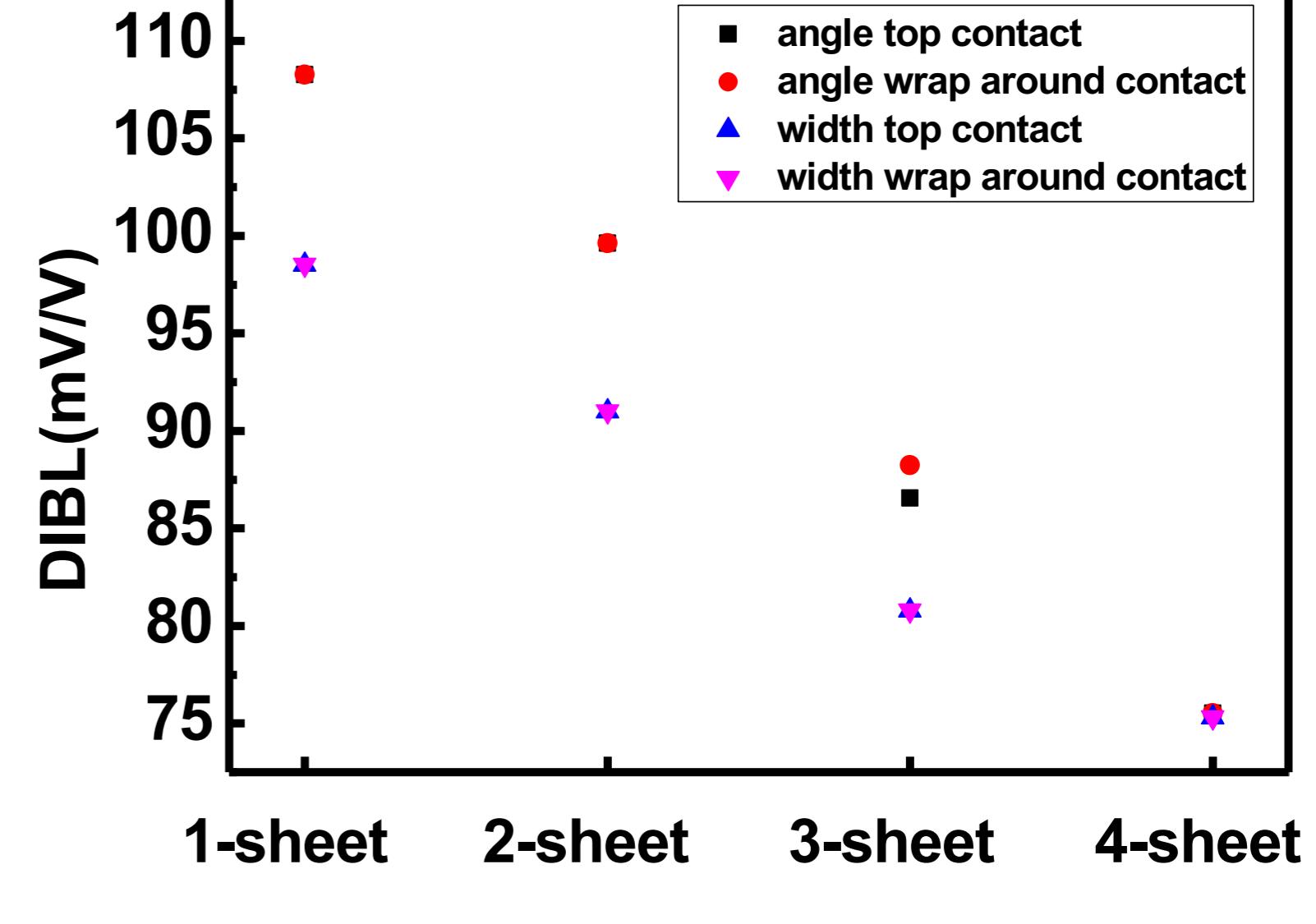

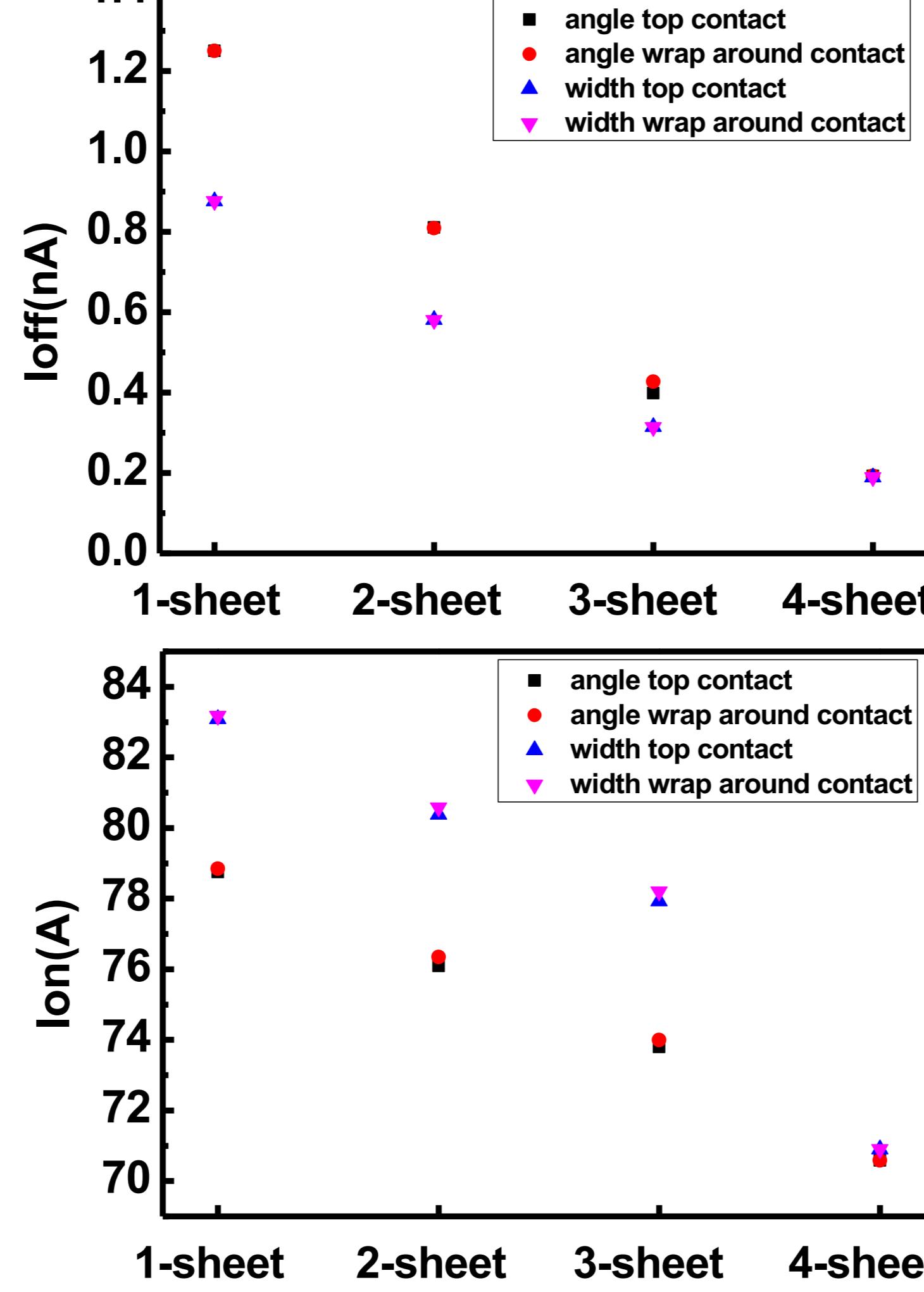

六、為更深入探討接觸區幾何對 GAAFET 電性的影響，本研究進一步模擬以下四種變因對元件效能的影響：

|                           |                           |

|---------------------------|---------------------------|

| Angle top contact         | Width top contact         |

| Angle wrap around contact | Width wrap around contact |

為了讓模擬更貼近實際製程與未來 1.5 nm 技術節點之預期，本研究在模擬參數上進行以下設定與校準：

- 有效氧化層厚度 (EOT) 設定為：0.6 nm 的  $\text{HfO}_2$  (高介電常數材料) + 0.8 nm 的  $\text{SiO}_2$ ，總厚度相當於實際先進製程中常見的複合閘極結構。此設計能更真實模擬閘極電容與短通道效應控制能力，符合 IRDS 的趨勢預測。

- 輽子遷移率 (mobility,  $\mu$ ) 設定為  $54 \text{ cm}^2/\text{V}\cdot\text{s}$ ，金屬閘極功函數 (workfunction) 設定為 4.42 eV，此為根據 IRDS 2023 Device Roadmap 進行之校準設定，使模擬所得的臨界電壓 ( $V_t$ ) 與導通電流 ( $I_{on}$ ) 更貼近實際預期，提升模擬數據之可信度與產業參考價值。

### (一) 不同奈米片層數下電性參數模擬數據

#### 1. $I_{ds}$ - $V_{gs}$ Curves

表 (五) 定 Angle/top contact 之不同奈米片層數 (1-4 sheet) GAAFET 模擬結果 。

|                            | 1sheet  | 2sheet | 3sheet | 4sheet |

|----------------------------|---------|--------|--------|--------|

| SS (mV/dec)                | 84.003  | 82.494 | 79.790 | 75.218 |

| $V_t,lin$ (V)              | 0.300   | 0.305  | 0.311  | 0.317  |

| $I_{on}$ ( $\mu\text{A}$ ) | 78.75   | 76.09  | 73.80  | 70.58  |

| $I_{off}$ (nA)             | 1.25    | 0.811  | 0.398  | 0.193  |

| DIBL(mV/V)                 | 108.257 | 99.625 | 86.550 | 75.516 |

表(六) 定 Angle/wrap around contact 之不同奈米片層數 (1~4 sheet) GAAFET 模擬結果。

|                | 1sheet  | 2sheet | 3sheet | 4sheet |

|----------------|---------|--------|--------|--------|

| SS (mV/dec)    | 84.002  | 82.492 | 80.164 | 77.323 |

| Vt,lin (V)     | 0.300   | 0.305  | 0.311  | 0.317  |

| Ion ( $\mu$ A) | 78.85   | 76.34  | 73.99  | 70.58  |

| Ioff (nA)      | 1.25    | 0.809  | 0.427  | 0.193  |

| DIBL(mV/V)     | 108.251 | 99.613 | 88.232 | 75.516 |

表(七) 定 extension width /top contact 之不同奈米片層數 (1~4 sheet) GAAFET 模擬結果。

|                | 1sheet | 2sheet | 3sheet | 4sheet |

|----------------|--------|--------|--------|--------|

| SS (mV/dec)    | 81.952 | 80.629 | 78.508 | 77.310 |

| Vt,lin (V)     | 0.246  | 0.256  | 0.267  | 0.276  |

| Ion ( $\mu$ A) | 83.09  | 80.38  | 77.93  | 70.90  |

| Ioff (nA)      | 0.876  | 0.581  | 0.315  | 0.189  |

| DIBL(mV/V)     | 98.513 | 91.001 | 80.793 | 75.322 |

表(八) 定 extension width /wrap around contact 之不同奈米片層數 (1~4 sheet) GAAFET 模擬結果。

|                | 1sheet | 2sheet | 3sheet | 4sheet |

|----------------|--------|--------|--------|--------|

| SS (mV/dec)    | 81.952 | 80.629 | 78.508 | 77.310 |

| Vt,lin (V)     | 0.246  | 0.256  | 0.267  | 0.276  |

| Ion ( $\mu$ A) | 83.09  | 80.38  | 77.93  | 70.90  |

| Ioff (nA)      | 0.876  | 0.581  | 0.315  | 0.189  |

| DIBL(mV/V)     | 98.513 | 91.001 | 80.793 | 75.322 |

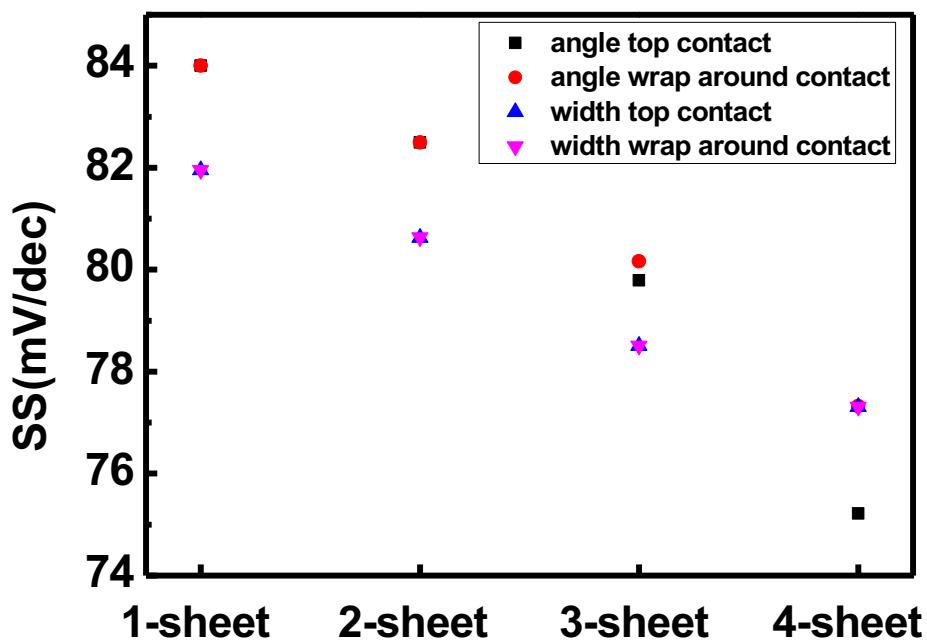

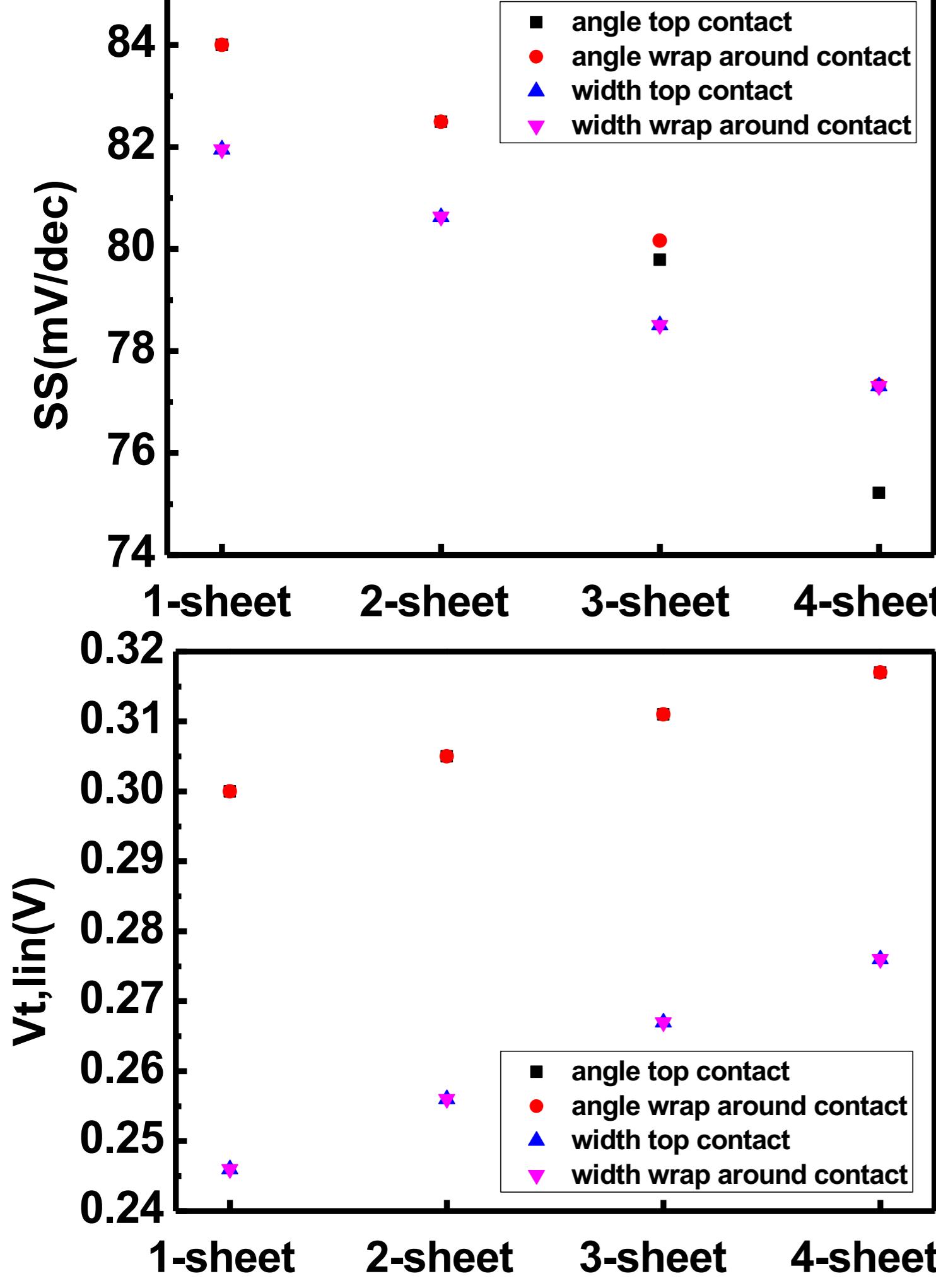

圖(二十) 不同接觸幾何條件下之次臨界擺幅 (SS) 比較圖

【收集 Sentaurus TCAD 模擬結果，並使用 Origin 軟體繪製成表格】

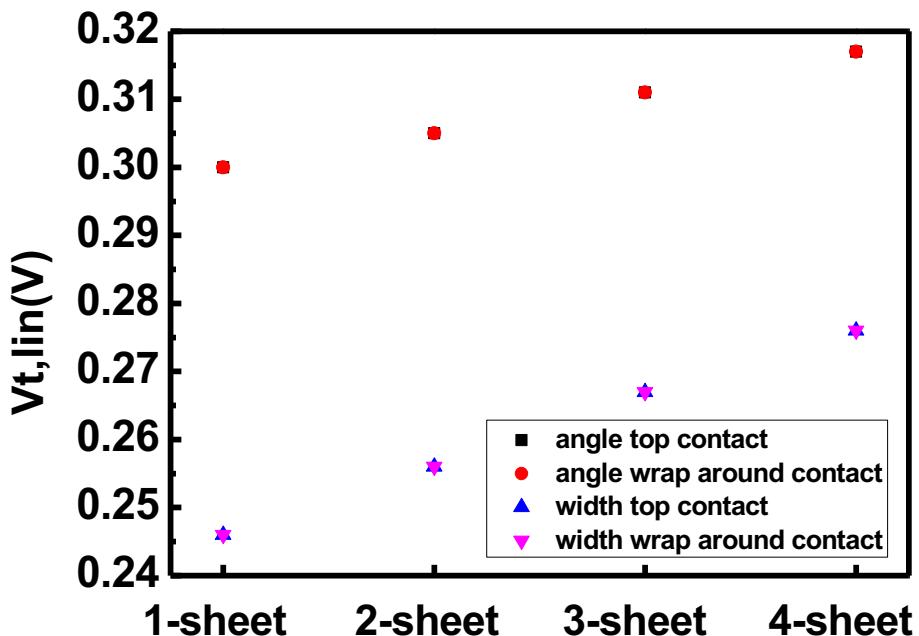

圖（二十一）不同接觸幾何條件下之臨界電壓（ $V_{t,lin}$ ）比較圖

【收集 Sentaurus TCAD 模擬結果，並使用 Origin 軟體繪製成表格】

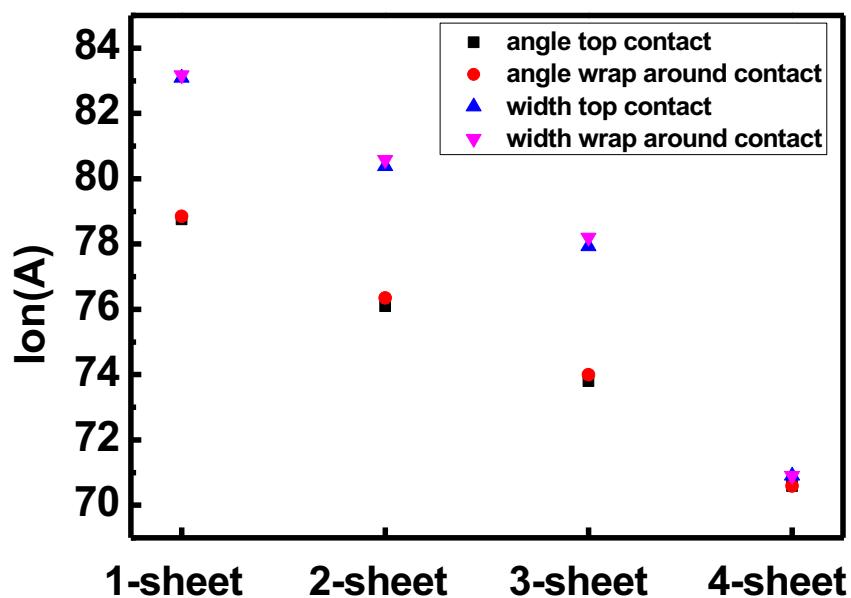

圖（二十二）不同接觸幾何條件下之導通電流（Ion）比較圖

【收集 Sentaurus TCAD 模擬結果，並使用 Origin 軟體繪製成表格】

圖（二十三）不同接觸幾何條件下之關斷電流（Ioff）比較圖

【收集 Sentaurus TCAD 模擬結果，並使用 Origin 軟體繪製成表格】

圖（二十四）不同接觸幾何條件下之 DIBL 效應比較圖

## 【收集 Sentaurus TCAD 模擬結果，並使用 Origin 軟體繪製成表格】

(二) 由模擬結果得知：

1. 導通電流 ( $I_{on}$ ) 在所有結構中，Width top contact 與 wrap around contact 組合的  $I_{on}$  最高（例如 1-sheet 為  $83.17 \mu A$ ），顯示適當的寬度設計有助於載子注入效率。

2. 次臨界擺幅 (SS) 和 DIBL 效應隨著奈米片數增加持續改善，width contact 設計組顯示出比 angle 設計更穩定的改善趨勢，反映其在通道控制與短通道抑制上的優勢。

3. 關斷電流 ( $I_{off}$ ) 在所有接觸幾何變化下皆顯著下降，其中寬度調整組 (top/wrap) 降幅最大，表現出更優秀的低功耗潛力。

4. 臨界電壓 ( $V_t$ ) 的提升趨勢則與導通電流減少密切相關，是設計調整中需權衡的項目。

## 伍、 討論

本研究依據 IRDS Roadmap 2023 提供的參數進行結構建立，並利用 Sentaurus TCAD 軟體模擬不同奈米片數量 (1-sheet、2-sheet、3-sheet、4-sheet) 對 GAAFET 電性參數的影響。模擬結果顯示，隨著奈米片層數的增加，GAAFET 的次臨界擺幅及 DIBL 均明顯改善，多層數結構對於抑制短通道效應具有顯著效果。臨界電壓的小幅提升則說明，雖然增加奈米片數可能會使元件需要略高的開啟電壓，但此舉同時提高了電壓控制的穩定性。

從導通電流與關斷電流的數值來看，儘管  $I_{on}$  大致穩定，但  $I_{off}$  隨著奈米片層數增加而大幅下降，使得元件在低功耗運作下具有更佳的能源效率。這一現象是因為增加的奈米片層數提供了更好的通道控制效果，有效阻隔漏電流的產生。

然而，內在延遲則隨著奈米片數的增加而上升，主要受到兩個因素影響。首先，奈米片層數增加可能會導致有效驅動電流下降，使得元件的開關速度略微降低。其次，多層奈米片結構會增加等效電容，使得充放電所需的時間延長，進一步影響電路的切換效率。因此，雖然增加奈米片層數有助於改善短通道效應與降低功耗，但同時也可能對開關速度產生影響，在實際設計時需在低功耗與高效能之間權衡取捨。

另外，由四種變因的比較得知，寬度優化（width contact）相較於角度優化（angle contact），在導通能力與短通道抑制方面具備更明顯的改善效果。本結果可作為未來設計 GAAFET 時，進一步優化接觸區結構與效能的依據。

## 陸、 結論

### 一、結論

本研究利用 Sentaurus TCAD 模擬不同奈米片數量 (1 – 4 sheets) 對 NSFET 電性影響，隨奈米片層數增加：

- (一) GAAFET 的次臨界擺幅及 DIBL 均明顯改善，多層數結構對於抑制短通道效應具有顯著效果。

- (二) 臨界電壓的小幅提升說明，雖然增加奈米片數可能會使元件需要略高的開啟電壓，但此舉同時提高了電壓控制的穩定性。

- (三) 從導通電流與關斷電流的數值來看，儘管  $I_{on}$  大致穩定，但  $I_{off}$  隨著奈米片層數增加而大幅下降，使得元件在低功耗運作下具有更佳的能源效率。這一現象是因為增加的奈米片層數提供了更好的通道控制效果，有效阻隔漏電流的產生。

### 二、未來展望

未來的工作將進一步分析四種不同變因下的本質延遲（Intrinsic Delay）。

## 柒、 參考文獻資料

- 一、 IRDS Roadmap 2023 International Roadmap for Devices and Systems."International Roadmap for Devices and Systems™ 2023 Edition." IEEE, 2023,<https://irds.ieee.org/editions/2023>.

- 二、 Loubet, N., et al. "Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET." 2017 IEEE Symposium on VLSI technology, 2017.

- 三、 胡璧合, "從摩爾定律看半導體產業近半世紀以來的發展", 科學月刊 2023-07-19

- 四、 Daewon Ha et al., "Energy-Efficient CMOS Scaling for 1nm and beyond." IEDM 2022 (SC1-2)

- 五、 [2] Es-Sakhi, Azzedin D. and Masud H. Chowdhury. "Analytical model to estimate the subthreshold swing of SOI FinFET." 2013 IEEE 20th International Conference on Electronics, Circuits, and Systems (ICECS) (2013):52-55.

- 六、 KUMAR, ASHISH. Analytical Modeling and Simulation Based Investigation of Newly Introduced Advanced TFET Architectures. Diss. AMITY UNIVERSITY UTTAR PRADESH, 2016.

## 【評語】052309

1. 作品使用電腦輔助設計(TCAD)軟體，對環繞式閘極奈米片場效應電晶體(NSFET)進行最佳化研究，對於奈米片層數增加所產生功耗及開關速度影響有一些結論，可供未來實際設計的參考。

2. 目前只使用電腦輔助設計(TCAD)軟體對現有系統進行效能評估，建議應有實驗成果的驗證及提出創新的設計。

3. 作品應對 Sentaurus TCAD 電腦輔助設計軟體，建議說明模擬所使用的學理及模擬方法。

4. 作品有說明晶片層幾何形狀，應進一步說明晶片結構層的材料及對應物理特性。

作品海報

# 前瞻奈米片場效電晶體設計之最佳化

[1]

隨著技術節點縮小至 2 nm 以下，鰭式場效電晶體 (FinFET) 面臨短通道效應與漏電流挑戰，環繞式閘極場效電晶體 (GAAFET) 因優異電流控制與低功耗成為主流。然而，進一步縮小至 1.5 nm 仍有製程與設計難題。

## 研究目的

探討在固定有效寬度 (Effective width) 及環繞式閘極垂直間距 (GAA Vertical Pitch) 下，改變奈米片的數量並調整相對元件參數，對 GAAFET 電性的影響。

- Effective Width

## 研究背景

### 關鍵技術名詞

有效驅動電流 ( $I_{eff}$ )、寄生電容 ( $C_{eff}$ )、次臨界擺幅 (Subthreshold Swing, SS)、短通道效應 (Short Channel Effects, SCE)。

- Subthreshold Swing (SS) [2]

- Short Channel Effect (SCE) [3]

## IRDS Roadmap 2023 Device Ground Rules

| YEAR OF PRODUCTION                   | 2028           |

|--------------------------------------|----------------|

| Logic industry "Node Range" Labeling | 2028-LGAA      |

| Fine-pitch 3D integration scheme     | G42M16         |

| Stacking                             | "1.5nm"        |

| Logic device structure options       | LGAA           |

| Backside structure options           | Direct contact |

| Platform device for logic            | LGAA           |

| LOGIC DEVICE GROUND RULES                             |       |

|-------------------------------------------------------|-------|

| Mx pitch (nm)                                         | 20    |

| M1 pitch (nm)                                         | 21    |

| M0 pitch (nm)                                         | 16    |

| Gate pitch (nm)                                       | 42    |

| Lg: Gate Length - HD (nm)                             | 12    |

| Lg: Gate Length - HP (nm)                             | 12    |

| Channel overlap ratio - two-sided                     | 0.20  |

| Spacer width (nm)                                     | 5     |

| Spacer k value                                        | 3.0   |

| Contact CD (nm) - finFET, LGAA                        | 20    |

| Device architecture key ground rules                  |       |

| Device lateral pitch (nm)                             | 24    |

| Device height (nm)                                    | 67    |

| FinFET Fin width (nm)                                 |       |

| Footprint drive efficiency - finFET                   |       |

| Lateral GAA vertical pitch (nm)                       | 17.0  |

| Lateral GAA (nanosheet) thickness (nm)                | 6.0   |

| Number of vertically stacked nanosheets on one device | 4     |

| LGA width (nm) - HP                                   | 20    |

| LGA width (nm) - HD                                   | 10    |

| LGA width (nm) - SRAM                                 | 6     |

| Footprint drive efficiency - lateral GAA - HP         | 5.47  |

| Device effective width (nm) - HP                      | 208.0 |

| Device effective width (nm) - HD                      | 128.0 |

| PN separation width (nm)                              | 30    |

| PN separation vertical space (nm)                     |       |

| YEAR OF PRODUCTION                   | 2028           |

|--------------------------------------|----------------|

| Logic industry "Node Range" Labeling | 2028-LGAA      |

| Fine-pitch 3D integration scheme     | G42M16         |

| Stacking                             | "1.5nm"        |

| Logic device structure options       | LGAA           |

| Backside structure options           | Direct contact |

| Platform device for logic            | LGAA           |

| LOGIC DEVICE ELECTRICAL SPECS                         |          |

|-------------------------------------------------------|----------|

| Power Supply Voltage - Vdd (V)                        | 0.60     |

| Subthreshold slope (mV/dec) - HP (mV/dec)             | 70       |

| Subthreshold slope (mV/dec) - HD (mV/dec)             | 67       |

| Capacitive equivalent thickness (CET) (nm) [2]        | 0.90     |

| Vt set (mV) at $I_{off}=10nA/\mu m$ - HP (mV)         | 164      |

| Vt set (mV) at $I_{off}=100pA/\mu m$ - HD (mV) [3][4] | 276      |

| Effective mobility (cm <sup>2</sup> /V.s)             | 80       |

| Rsd (Ohms.μm) [5]                                     | 245      |

| Balisticity injection velocity (cm/s)                 | 9.00E+06 |

| Vdsat (V) - HP                                        | 0.108    |

| Vdsat (V) - HD                                        | 0.198    |

| Ion (μA/μm) at $I_{off}=10nA/\mu m$ - HP [6]          | 759      |

| Ion (μA/device) at $I_{off}=10nA/\mu m$ - HP [7]      | 158      |

| Ion (μA/μm) at $I_{off}=100pA/\mu m$ - HD [8]         | 546      |

| Ion (μA/device) at $I_{off}=100pA/\mu m$ - HD [9]     | 114      |

| Coh total (fF/μm <sup>2</sup> ) - HP/HD [8]           | 38.35    |

| Gate height over fin (nm)                             | 10       |

| Coh (fF/μm <sup>2</sup> ) - HP [8]                    | 0.37     |

| Coh (fF/μm <sup>2</sup> ) - HD [8]                    | 0.37     |

| CW1 (ps) - FO3 load, HP [9]                           | 0.87     |

| Y(CV) (1/pS) - FO3 load, HP [10]                      | 1.15     |

| Energy per switching [CV2] (fJ/switch) - FO3 load, HP | 0.40     |

[4]

1. Device Architecture and Ground Rules Roadmap for Logic Devices (邏輯元件的架構與製程基準路線圖)

2. Projected Electrical Specifications of Logic Core Device (邏輯核心元件的預測電性規格)

圖為 IRDS Roadmap 2023 Device Ground Rules 之擷取。

## Sentaurus TCAD

圖為 Sentaurus TCAD 介面，右圖顯示不同通道數量之三維 NSFET 結構。

Sentaurus TCAD 可預測元件電性、比較不同結構優劣，並評估製程對元件特性的影響。

# 研究方法

## 結果與討論

### • GAAFET Parameters

|                                      |           |    |    |    |

|--------------------------------------|-----------|----|----|----|

| 閘極長度 (nm)                            | 12        |    |    |    |

| 奈米片層數                                | 1         | 2  | 3  | 4  |

| 奈米片厚度 (nm)                           | 6         |    |    |    |

| 奈米片垂直間距 (nm)                         | 17        |    |    |    |

| 奈米片寬度 (nm)                           | 58        | 26 | 15 | 10 |

| 奈米片等效寬度 (nm)                         | 128       |    |    |    |

| 等效氧化物厚度 (nm)                         | 0.7       |    |    |    |

| 通道摻雜濃度 ( $\text{cm}^{-3}$ ) (硼摻雜)    | $10^{16}$ |    |    |    |

| 汲極/源極摻雜濃度 ( $\text{cm}^{-3}$ ) (砷摻雜) | $10^{21}$ |    |    |    |

| 基板摻雜濃度 ( $\text{cm}^{-3}$ ) (硼摻雜)    | $10^{19}$ |    |    |    |

### • 不同奈米片數 GAAFET 結構

### • $I_{ds}-V_{gs}$ 電流電壓特性圖

Work function = 4.35 eV      Vdd = 0.6 V

|                            | 1-sheet  | 2-sheet | 3-sheet | 4-sheet |

|----------------------------|----------|---------|---------|---------|

| $I_{on}$ ( $\mu\text{A}$ ) | 56.83    | 55.91   | 55.41   | ★ 55.38 |

| DIBL (mV/V)                | ★ 76.588 | 70.595  | 63.159  | 54.514  |

| SS (mV/dec)                | ★ 79.954 | 78.811  | 77.055  | 74.768  |

| $V_{t,lin}$ (V)            | 0.246    | 0.251   | 0.256   | ★ 0.261 |

| $I_{off}$ (nA)             | 2.871    | 2.025   | 1.247   | ★ 0.680 |

### • 1-sheet與4-sheet結構在汲極磊晶剖面下的電壓壓降與磊晶高度關係之比較

### • Conduct Band Diagram along Channel

## Intrinsic Delay

Work function = 4.35 eV Vdd = 0.6 V

|                            | 1sheet  | 2sheet  | 3sheet | 4sheet |

|----------------------------|---------|---------|--------|--------|

| I <sub>eff</sub> (μA)      | ★ 27.46 | 27.01   | 26.79  | 26.00  |

| C <sub>eff</sub> (fF)      | 0.170   | ★ 0.169 | 0.221  | 0.251  |

| Intrinsic Delay (ps)       | ★ 37.1  | 37.5    | 49.5   | 58.0   |

| 源極汲極磊晶面積(nm <sup>2</sup> ) | 1902    | ★ 1887  | 2312   | 3000   |

$$\tau = \frac{C_{eff} \times V_{DD}}{I_{eff}}$$

## 新的四種變因

- EOT=0.6 nm 的 HfO<sub>2</sub> (高介電常數材料) + 0.8 nm 的 SiO<sub>2</sub>。

- 載子遷移率 (mobility, μ) 設定為 54 cm<sup>2</sup>/V·s, 金屬閘極功函數 (workfunction) 設定為 4.42 eV。

### Angle/top contact

|                        | 1sheet  | 2sheet | 3sheet | 4sheet   |

|------------------------|---------|--------|--------|----------|

| SS (mV/dec)            | 84.003  | 82.494 | 79.790 | ★ 75.218 |

| V <sub>t,lin</sub> (V) | ★ 0.300 | 0.305  | 0.311  | 0.317    |

| I <sub>on</sub> (μA)   | ★ 78.75 | 76.09  | 73.80  | 70.58    |

| I <sub>off</sub> (nA)  | 1.25    | 0.811  | 0.398  | ★ 0.193  |

| DIBL(mV/V)             | 108.257 | 99.625 | 86.550 | ★ 75.516 |

### Extension width/top contact

|                        | 1sheet  | 2sheet | 3sheet | 4sheet   |

|------------------------|---------|--------|--------|----------|

| SS (mV/dec)            | 81.952  | 80.629 | 78.508 | ★ 77.310 |

| V <sub>t,lin</sub> (V) | ★ 0.246 | 0.256  | 0.267  | 0.276    |

| I <sub>on</sub> (μA)   | ★ 83.09 | 80.38  | 77.93  | 70.90    |

| I <sub>off</sub> (nA)  | 0.876   | 0.581  | 0.315  | ★ 0.189  |

| DIBL(mV/V)             | 98.513  | 91.001 | 80.793 | ★ 75.322 |

### Angle/wrap around contact

|                        | 1sheet  | 2sheet | 3sheet | 4sheet   |

|------------------------|---------|--------|--------|----------|

| SS (mV/dec)            | 84.002  | 82.492 | 80.164 | ★ 77.323 |

| V <sub>t,lin</sub> (V) | ★ 0.300 | 0.305  | 0.311  | 0.317    |

| I <sub>on</sub> (μA)   | ★ 78.85 | 76.34  | 73.99  | 70.58    |

| I <sub>off</sub> (nA)  | 1.25    | 0.809  | 0.427  | ★ 0.193  |

| DIBL(mV/V)             | 108.251 | 99.613 | 88.232 | ★ 75.516 |

### Extension width/wrap around contact

|                        | 1sheet  | 2sheet | 3sheet | 4sheet   |

|------------------------|---------|--------|--------|----------|

| SS (mV/dec)            | 81.953  | 80.635 | 78.511 | ★ 77.310 |

| V <sub>t,lin</sub> (V) | ★ 0.246 | 0.256  | 0.267  | 0.276    |

| I <sub>on</sub> (μA)   | ★ 83.17 | 80.58  | 78.20  | 70.90    |

| I <sub>off</sub> (nA)  | 0.876   | 0.580  | 0.314  | ★ 0.189  |

| DIBL(mV/V)             | 98.515  | 91.005 | 80.779 | ★ 75.322 |

## 結論

模擬結果顯示，隨著奈米片層數的增加，GAAFET 的次臨界擺幅及 DIBL 均明顯改善，多層數結構對於抑制短通道效應具有顯著效果。臨界電壓的小幅提升則說明，雖然增加奈米片數可能會使元件需要略高的開啟電壓，但此舉同時提高了電壓控制的穩定性。

從導通電流與關斷電流的數值來看，儘管 I<sub>on</sub> 大致穩定，但 I<sub>off</sub> 隨著奈米片層數增加而大幅下降，使得元件在低功耗運作下具有更佳的能源效率。這一現象是因為增加的奈米片層數提供了更好的通道控制效果，有效阻隔漏電流的產生。

## 參考資料

- [1] Evolution of logic devices. Reproduced with permission.[30] Copyright 2022, IEEE.

[2] Es-Sakhi, Azzedin D. and Masud H. Chowdhury. "Analytical model to estimate the subthreshold swing of SOI FinFET." 2013 IEEE 20th International Conference on Electronics, Circuits, and Systems (ICECS) (2013):52-55.

[3] KUMAR, ASHISH. Analytical Modeling and Simulation Based Investigation of Newly Introduced Advanced TFET Architectures. Diss. AMITY UNIVERSITY UTTAR PRADESH, 2016.

[4] IRDS Roadmap 2023

[5] 胡璧合, "從摩爾定律看半導體產業近半世紀以來的發展", 科學月刊2023-07-19

[6] Lobet, N., et al. "Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET." 2017 IEEE Symposium on VLSI technology, 2017.

其餘未標示之圖皆由作者繪製